National Instruments PC-LPM-16/PnP User Manual

Page 62

Appendix C Using Your PC-LPM-16 (Non-PnP) Board

PC-LPM-16/PnP User Manual

C-2

National Instruments Corporation

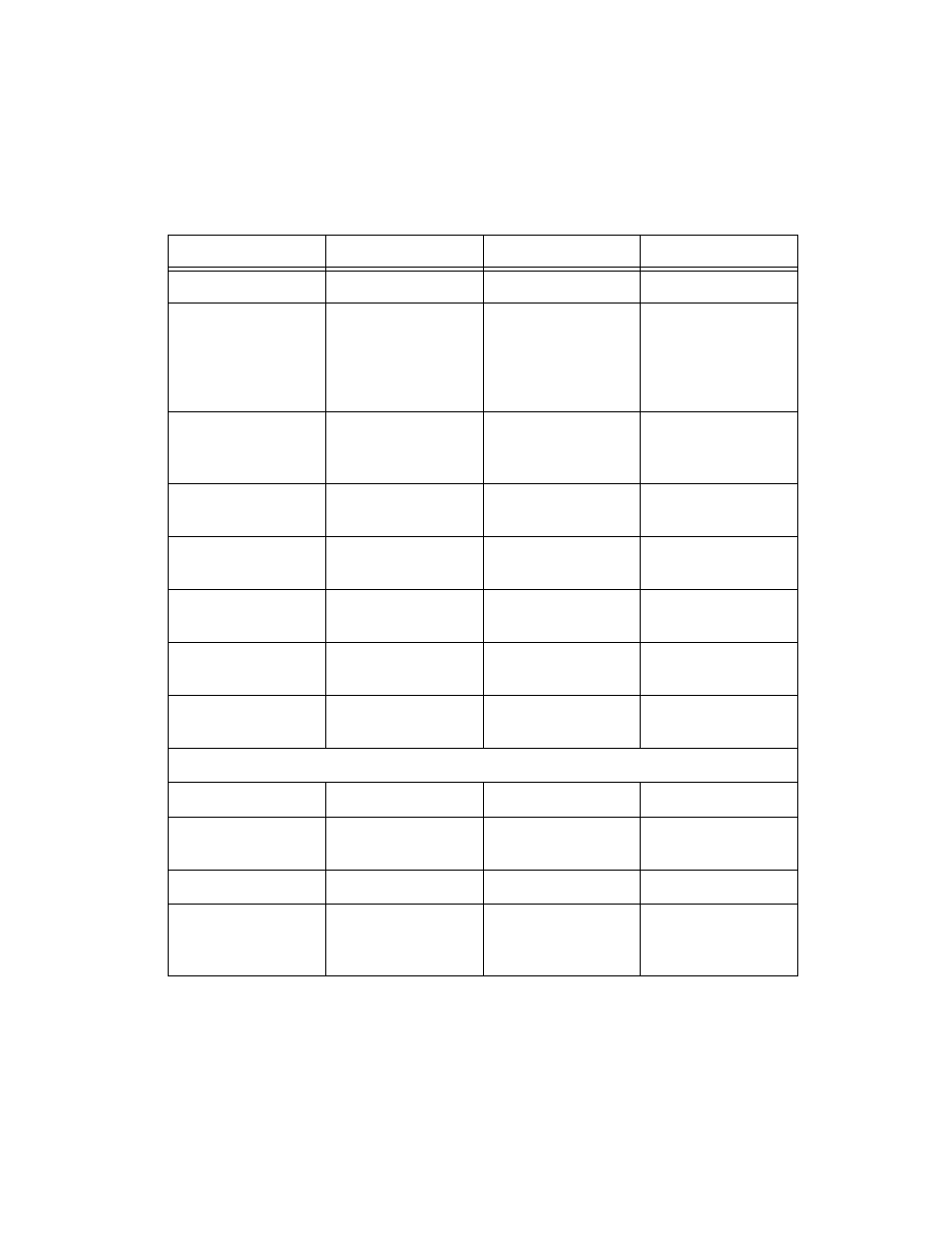

Data FIFO Size

16 words

512 words

256 words

Dummy reads to A/D

and FIFO high-byte

and low-byte registers

after clearing data

FIFO

Required

Not required, but

allowed

Not required, but

allowed

ADC FIFO Data

Reading Order

Low byte before

high byte preferred

Low byte must be

read before high

byte

Low byte must be

read before high

byte

Overflow Error Bit

Location

Status Register 1,

bit 1

Status Register 1,

bit 1

Status Register 2,

bit 1

Overrun Error Bit

Location

Not implemented

Not implemented

Status Register 2,

bit 0

Data Error Bit

Location

Not implemented

Not implemented

Status Register 1,

bit 1

5 and 12 V Supply

Fuses

Nonresettable

Self-resetting

Self-resetting

-12 V Supply Power

Requirements

0 mA

15 mA typ

15 mA typ

Performance Specification Changes

INL

±

1 LSB max

±

0.5 LSB max

±

0.5 LSB max

Gain Error,

±

2.8 V or

to 10 V Range

±

3 LSB typ,

±

7 LSB max

±

2 LSB typ,

±

4 LSB max

±

2 LSB typ,

±

4 LSB max

Calibration Time

700

µ

s typ

10 ms typ

10 ms typ

Overvoltage

Protection or Analog

Input Powered Off

±

45 V

±

35 V

±

35 V

Table C-1.

Comparison of Characteristics (Continued)

Functional Changes

Legacy PC-LPM-16

Revised PC-LPM-16

PC-LPM-16PnP