Figure 2-5 two-book system ring structure, Book 0 book 3 book 1 book 2, Jumper book – IBM 990 User Manual

Page 42: Ring structure

30

IBM

^

zSeries 990 Technical Guide

Figure 2-4 Concentric ring structure

A memory-coherent director optimizes ring traffic and filters out cache traffic by not looking on

the ring for cache hits in other books if it is certain that the resources for a given logical

partition exists in the same book.

The Level 2 (L2) cache is implemented on four cache (SD) chips. Each SD chip holds 8 MB,

resulting in a 32 MB L2 cache per book. The L2 cache is shared by all PUs in the book and

has a store-in buffer design. The connection to processor memory is done through four

high-speed memory buses.

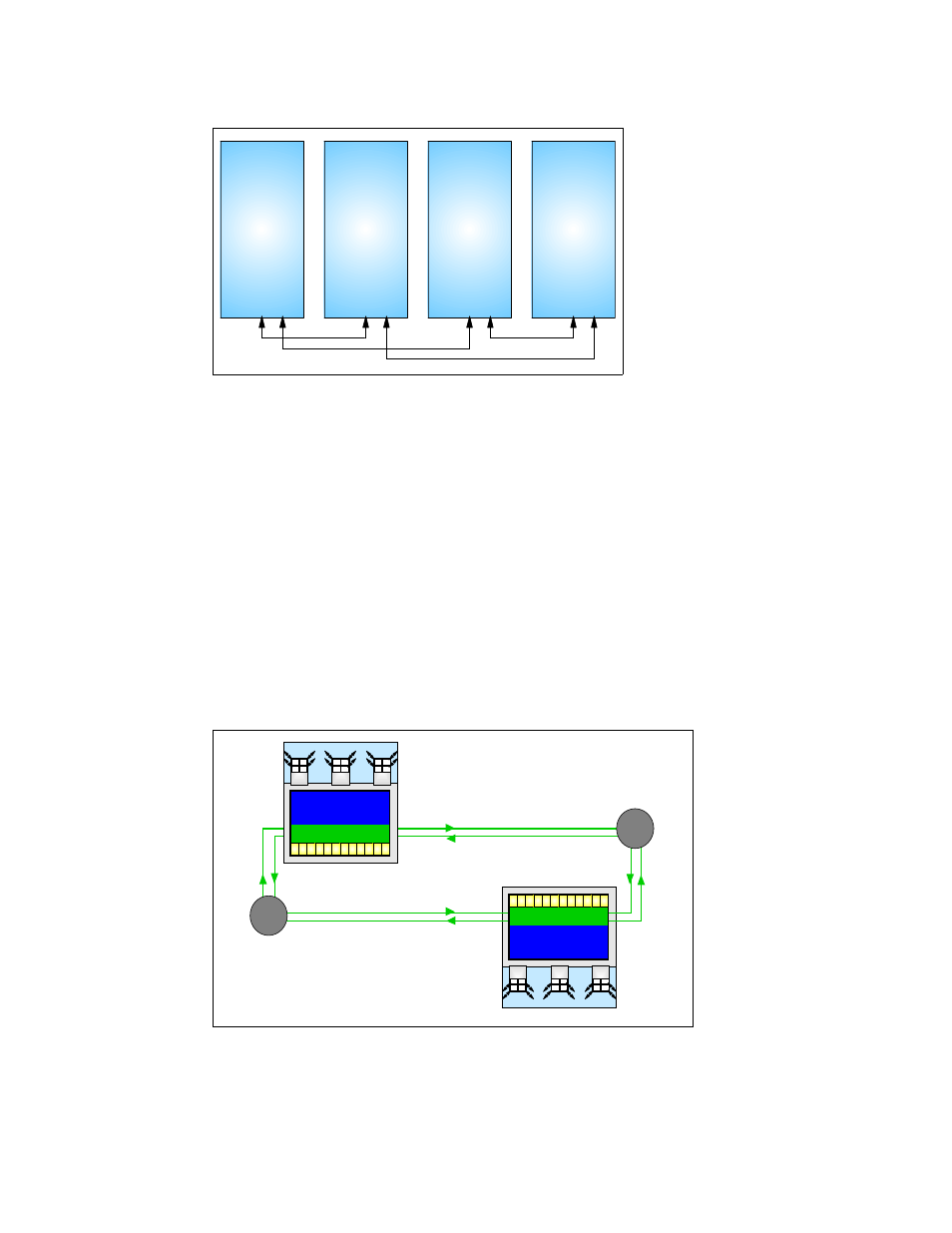

There is a ring structure within which the books maintain interbook communication at the L2

cache level. Additional books extend the function of the ring structure for interbook

communication. The ring topology is shown in Figure 2-5 and Figure 2-6 on page 31, and in

Figure 2-7 on page 31.

A book jumper completes the ring in order to be able to insert additional books into the ring

non-disruptively.

Figure 2-5 Two-book system ring structure

Book 0

Book 3

Book 1

Book 2

Jumper Book

STI

MBA

STI

STI

STI

STI

MBA

STI

STI

STI

4 x 2.5 GB/S

4 x 2.5 GB/S

STI

MBA

STI

STI

STI

4 x 2.5 GB/S

Ring Structure

PU

PU

PU

PU

PU PU

PU

PU PU PU

PU

PU

Jumper Book

STI

MBA

STI

STI

STI

STI

MBA

STI

STI

STI

4 x 2 GB/S

4 x 2 GB/S

STI

MBA

STI

STI

STI

4 x 2 GB/S

MBA Card

PU

PU

PU

PU

PU PU

PU

PU PU PU PU

PU

Level 2 Cache 32MB

MCM

MCM

Memory Up to 64GB

Level 2 Cache 32MB

Level 2 Cache 32MB

Memory Up to 64GB

MCM

MCM