0°c to +70°c; v, 5v ±10%) – Maxim Integrated DS5001FP User Manual

Page 13

DS5001FP

13 of 26

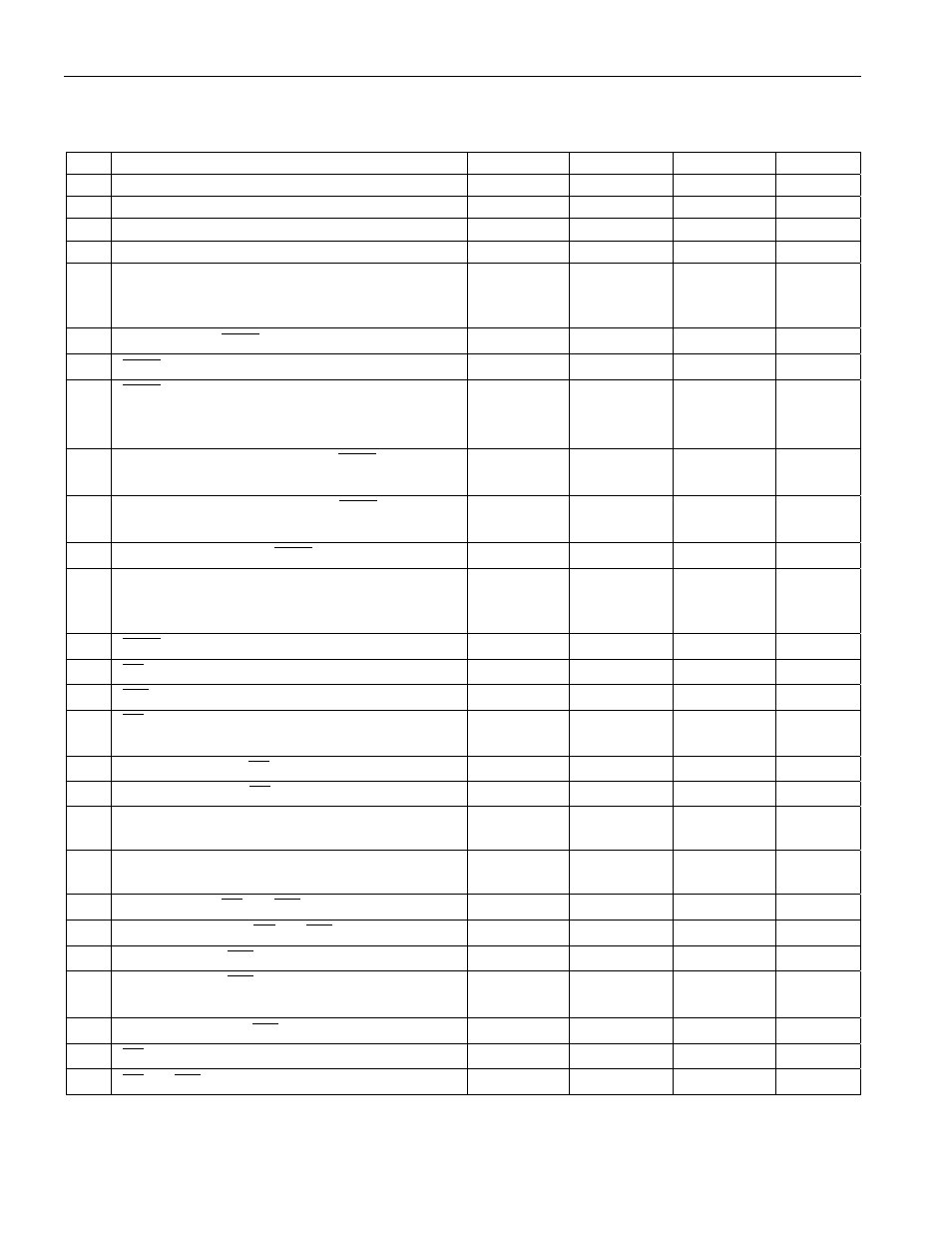

AC CHARACTERISTICS

EXPANDED BUS MODE TIMING SPECIFICATIONS

(T

A

= 0°C to +70°C; V

CC

= 5V ±10%)

#

PARAMETER

SYMBOL

MIN

MAX

UNITS

1

Oscillator Frequency

1/ t

CLK

1.0

16

MHz

2

ALE Pulse Width

t

ALPW

2t

CLK

- 40

ns

3

Address Valid to ALE Low

t

AVALL

t

CLK

- 40

ns

4

Address Hold After ALE Low

t

AVAAV

t

CLK

- 35

ns

5

ALE Low to Valid Instruction In

at 12MHz

at 16MHz

t

ALLVI

4t

CLK

- 150

4t

CLK

- 90

ns

ns

6

ALE Low to

PSEN

Low

t

ALLPSL

t

CLK

- 25

ns

7

PSEN

Pulse Width

t

PSPW

3t

CLK

- 35

ns

8

PSEN

Low to Valid Instruction In

at 12MHz

at 16MHz

t

PSLVI

3t

CLK

- 150

3t

CLK

- 90

ns

ns

9

Input Instruction Hold After

PSEN

Going

High

t

PSIV

0

ns

10

Input Instruction Float After

PSEN

Going

High

t

PSIX

t

CLK

- 20

ns

11

Address Hold After

PSEN

Going High

t

PSAV

t

CLK

- 8

ns

12

Address Valid to Valid Instruction In

at 12MHz

at 16MHz

t

AVVI

5t

CLK

- 150

5t

CLK

- 90

ns

ns

13

PSEN

Low to Address Float

t

PSLAZ

0

ns

14

RD

Pulse Width

t

RDPW

6t

CLK

- 100

ns

15

WR

Pulse Width

t

WRPW

6t

CLK

- 100

ns

16

RD

Low to Valid Data In

at 12MHz

at 16MHz

t

RDLDV

5t

CLK

- 165

5t

CLK

- 105

ns

ns

17

Data Hold After

RD

High

t

RDHDV

0

ns

18

Data Float After

RD

High

t

RDHDZ

2t

CLK

- 70

ns

19

ALE Low to Valid Data In at 12MHz

at 16MHz

t

ALLVD

8t

CLK

- 150

8t

CLK

- 90

ns

20

Valid Address to Valid Data In at 12MHz

at 16MHz

t

AVDV

9t

CLK

- 165

9t

CLK

- 105

ns

21

ALE Low to

RD

or

WR

Low

t

ALLRDL

3t

CLK

- 50

3t

CLK

+ 50

ns

22

Address Valid to

RD

or

WR

Low

t

AVRDL

4t

CLK

- 130

ns

23

Data Valid to

WR

Going Low

t

DVWRL

t

CLK

- 60

ns

24

Data Valid to

WR

High

at 12MHz

at 16MHz

t

DVWRH

7t

CLK

- 150

7t

CLK

- 90

ns

25

Data Valid After

WR

High

t

WRHDV

t

CLK

- 50

ns

26

RD

Low to Address Float

t

RDLAZ

0

ns

27

RD

or

WR

High to ALE High

t

RDHALH

t

CLK

- 40

t

CLK

+ 50

ns