Maxim Integrated DS5001FP User Manual

Page 10

DS5001FP

10 of 26

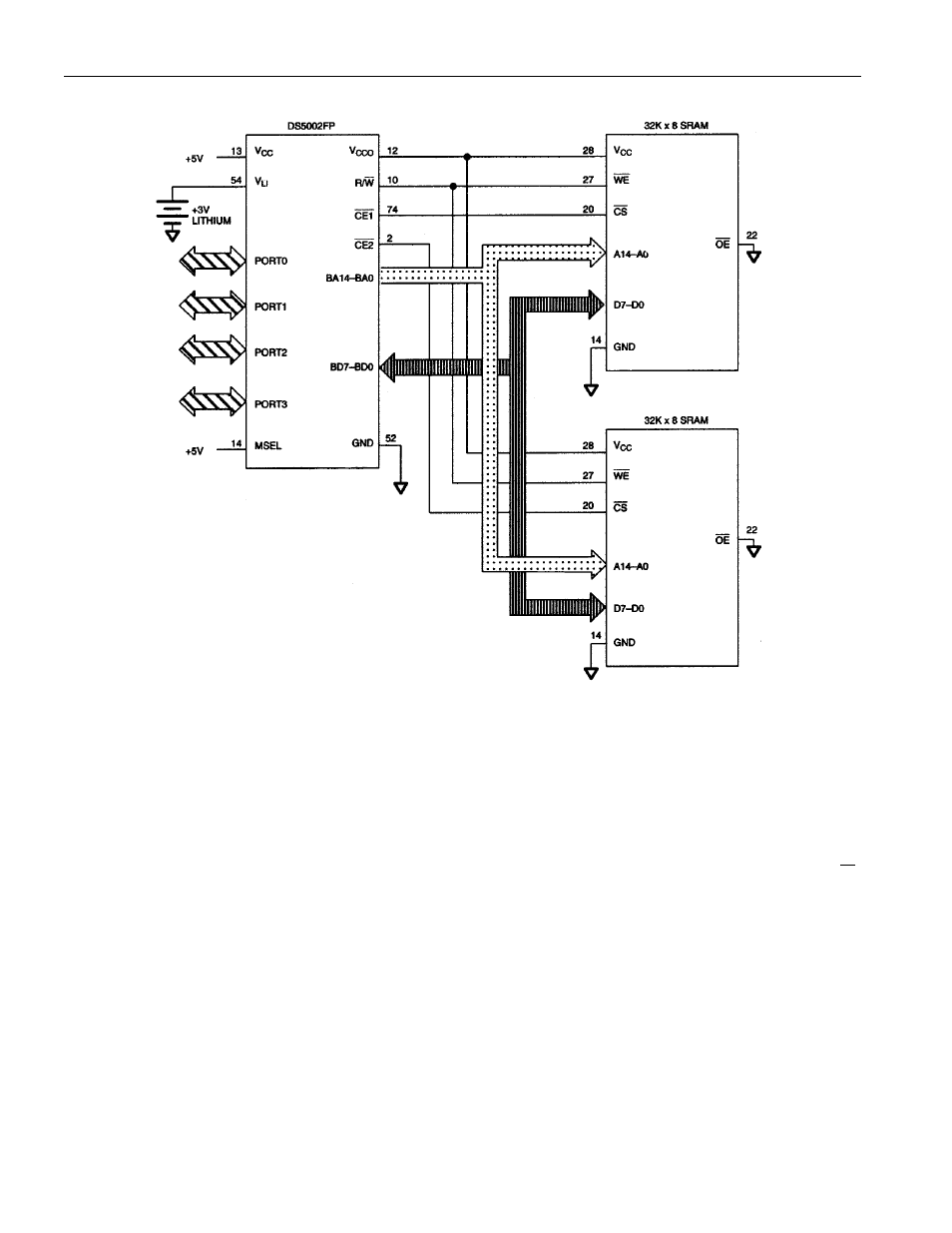

Figure 6. DS5001FP CONNECTION TO 64k x 8 SRAM

POWER MANAGEMENT

The DS5001FP monitors V

CC

to provide power-fail reset, early warning power-fail interrupt, and switch

over to lithium backup. It uses an internal bandgap reference in determining the switch points. These are

called V

PFW

, V

CCMIN

, and V

LI

, respectively. When V

CC

drops below V

PFW

, the DS5001FP performs an

interrupt vector to location 2Bh if the power-fail warning was enabled. Full processor operation continues

regardless. When power falls further to V

CCMIN

, the DS5001FP invokes a reset state. No further code

execution is performed unless power rises back above V

CCMIN

. All decoded chip enables and the R/

W

signal go to an inactive (logic 1) state. V

CC

is still the power source at this time. When V

CC

drops further

to below V

LI

, internal circuitry switches to the lithium cell for power. The majority of internal circuits are

disabled and the remaining nonvolatile states are retained. Any devices connected V

CCO

are powered by

the lithium cell at this time. V

CCO

is at the lithium battery voltage minus approximately 0.45V. This drop

varies depending on the load. Low power SRAMs should be used for this reason. When using the

DS5001FP, the user must select the appropriate battery to match the RAM data retention current and the

desired backup lifetime. Note that the lithium cell is only loaded when V

CC

< V

LI

. The User’s Guide has

more information on this topic. The trip points V

CCMIN

and V

PFW

are listed in Electrical Specifications.