FUJITSU MPE3XXXAT User Manual

Page 74

C141-E077-01EN

5 - 7

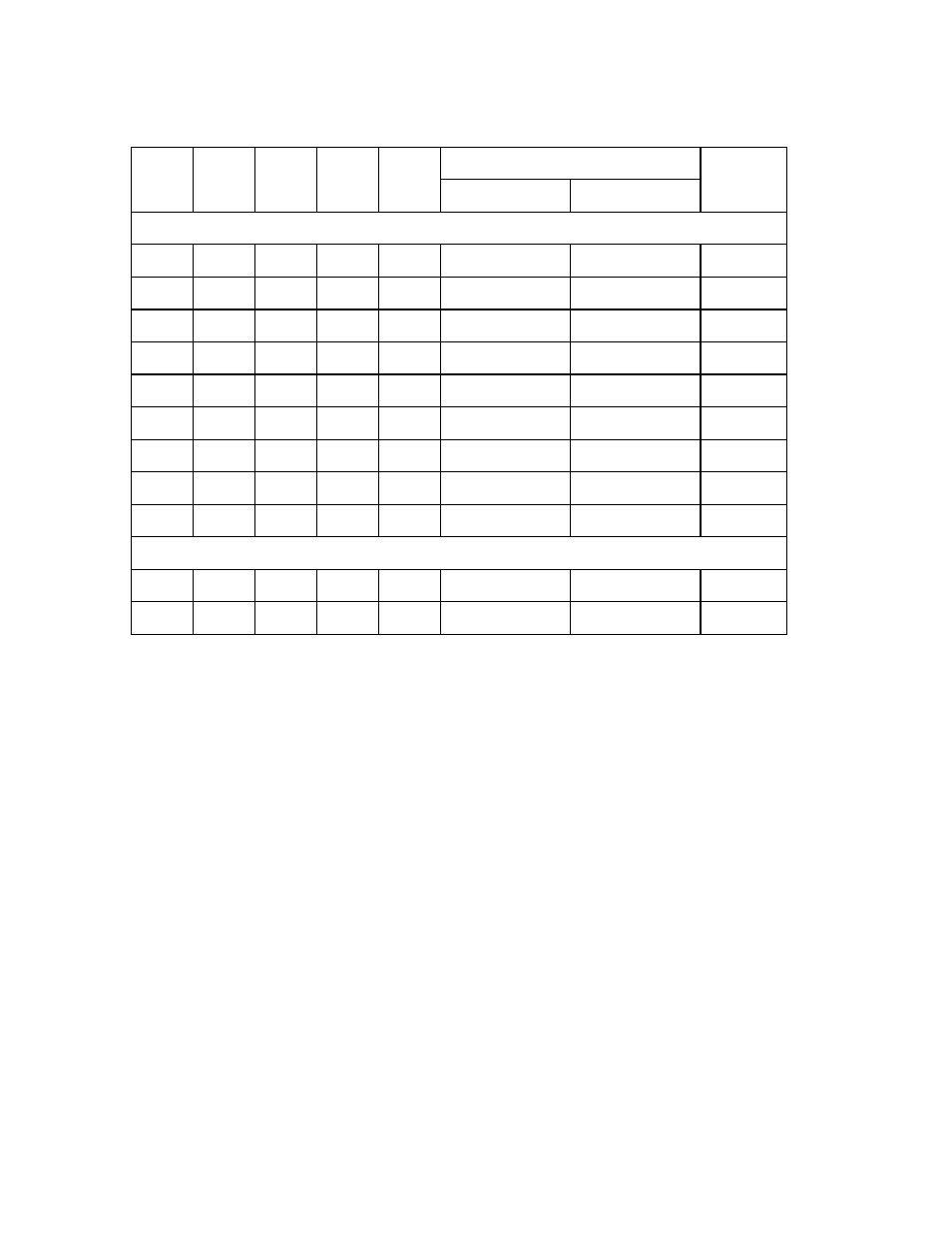

Table 5.3

I/O registers

I/O registers

Read operation

Write operation

Command block registers

1

0

0

0

0

Data

Data

X'1F0'

1

0

0

0

1

Error Register

Features

X'1F1'

1

0

0

1

0

Sector Count

Sector Count

X'1F2'

1

0

0

1

1

Sector Number

Sector Number

X'1F3'

1

0

1

0

0

Cylinder Low

Cylinder Low

X'1F4'

1

0

1

0

1

Cylinder High

Cylinder High

X'1F5'

1

0

1

1

0

Device/Head

Device/Head

X'1F6'

1

0

1

1

1

Status

Command

X'1F7'

1

1

X

X

X

(Invalid)

(Invalid)

—

Control block registers

0

1

1

1

0

Alternate Status

Device Control

X'3F6'

0

1

1

1

1

—

—

X'3F7'

Notes:

1.

The Data register for read or write operation can be accessed by 16 bit data bus

(DATA0 to DATA15).

2.

The registers for read or write operation other than the Data registers can be accessed

by 8 bit data bus (DATA0 to DATA7).

3.

When reading the Drive Address register, bit 7 is high-impedance state.

4.

The LBA mode is specified, the Device/Head, Cylinder High, Cylinder Low, and

Sector Number registers indicate LBA bits 27 to 24, 23 to 16, 15 to 8, and 7 to 0.

Host I/O

address

DA0

DA1

DA2

CS1–

CS0–

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)