2 multiword data transfer – FUJITSU MPE3XXXAT User Manual

Page 153

C141-E077-01EN

5 - 86

5.6.2

Multiword data transfer

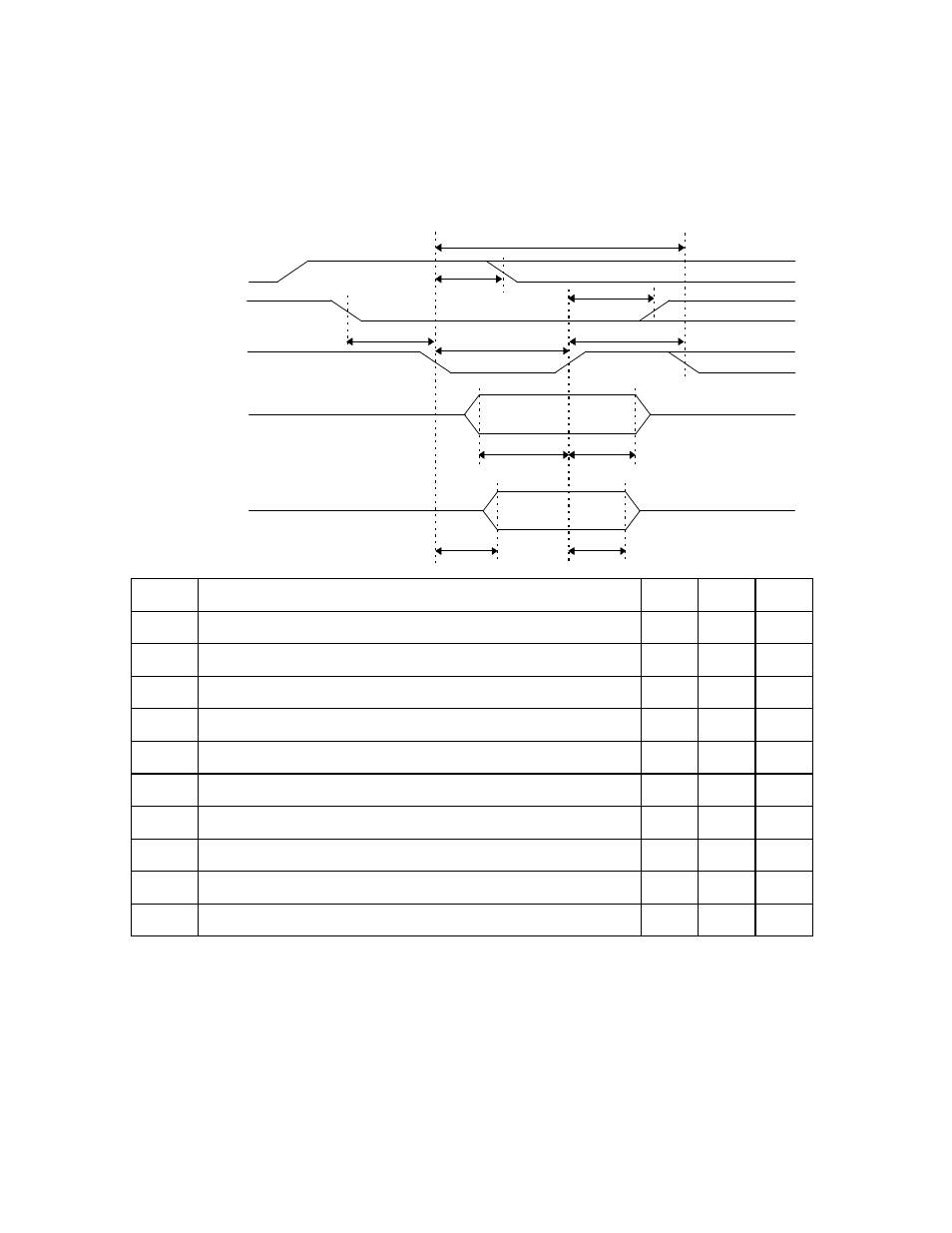

Figure 5.9 shows the multiword DMA data transfer timing between the device and the host

system.

tF

tE

tH

tG

tJ

tD

tI

tC

t0

Read data

DD0-DD15

Write data

DD0-DD15

DIOR-/DIOW-

DMACK-

DMARQ

tK

Symbol

Timing parameter

Min.

Max.

Unit

t0

Cycle time

120

—

ns

tC

Delay time from DMACK assertion to DMARQ negation

—

35

ns

tD

Pulse width of DIOR-/DIOW-

70

—

ns

tE

Data setup time for DIOR-

—

30

ns

tF

Data hold time for DIOR-

5

—

ns

tG

Data setup time for DIOW-

20

—

ns

tH

Data hold time for DIOW-

10

—

ns

tI

DMACK setup time for DIOR-/DIOW-

0

—

ns

tJ

DMACK hold time for DIOR-/DIOW-

5

—

ns

tK

Continuous time of high level for DIOR-/DIOW-

25

—

ns

Figure 5.9

Multiword DMA data transfer timing (mode 2)

See also other documents in the category FUJITSU Hardware:

- XG Series P3NK-4452-01ENZD (614 pages)

- FPCAC14C (1 page)

- MCJ3230SS (161 pages)

- MBA3073NC (138 pages)

- T5140 (102 pages)

- T5140 (76 pages)

- MAM3367MC/MP (152 pages)

- MPC3045AH (185 pages)

- MB2142-02 (23 pages)

- MB15F86UL (6 pages)

- MHS2030AT (40 pages)

- MHW2100BS (296 pages)

- MHK2060AT (227 pages)

- Disk Drives MHK2060AT (227 pages)

- MCM3064SS (170 pages)

- Mainboard D1561 (45 pages)

- MHC2040AT (219 pages)

- D1961 (45 pages)

- DISK DRIVES MHM2100AT (231 pages)

- MHR2010AT (250 pages)

- MHZ2120BJ (320 pages)

- MCE3064AP (175 pages)

- LQFP-64P (16 pages)

- Solaris PCI GigabitEthernet 3.0 (115 pages)

- MAY2036RC (94 pages)

- MAB3091 (142 pages)

- MHV2040AH (40 pages)

- MHW2040AC (278 pages)

- ETERNUSmgr P2X0-0202-01EN (64 pages)

- VSS Hardware Provider 2.1 (134 pages)

- MAG3182FC (61 pages)

- MAU3147NC/NP (130 pages)

- MAX3147RC (94 pages)

- MHV2160BT (296 pages)

- MHV2040AT (280 pages)

- MAW3300NC/NP (130 pages)

- DeskPower E623 (50 pages)

- MAG3182LC (133 pages)

- OPTICAL DISK DRIVES MDG3064UB (42 pages)

- MHF2021AT (225 pages)

- MHR2040AT (40 pages)

- Single Drive FTM7926FB (1 page)

- PG-FCS103 (98 pages)

- MAS3735FC (114 pages)