Ide configuration registers, Ide bus master control registers, 1 ide configuration registers – HP D315 User Manual

Page 84: 2 ide bus master control registers

Chapter 5 Input/Output Interfaces

5.2.1.1 IDE

Configuration Registers

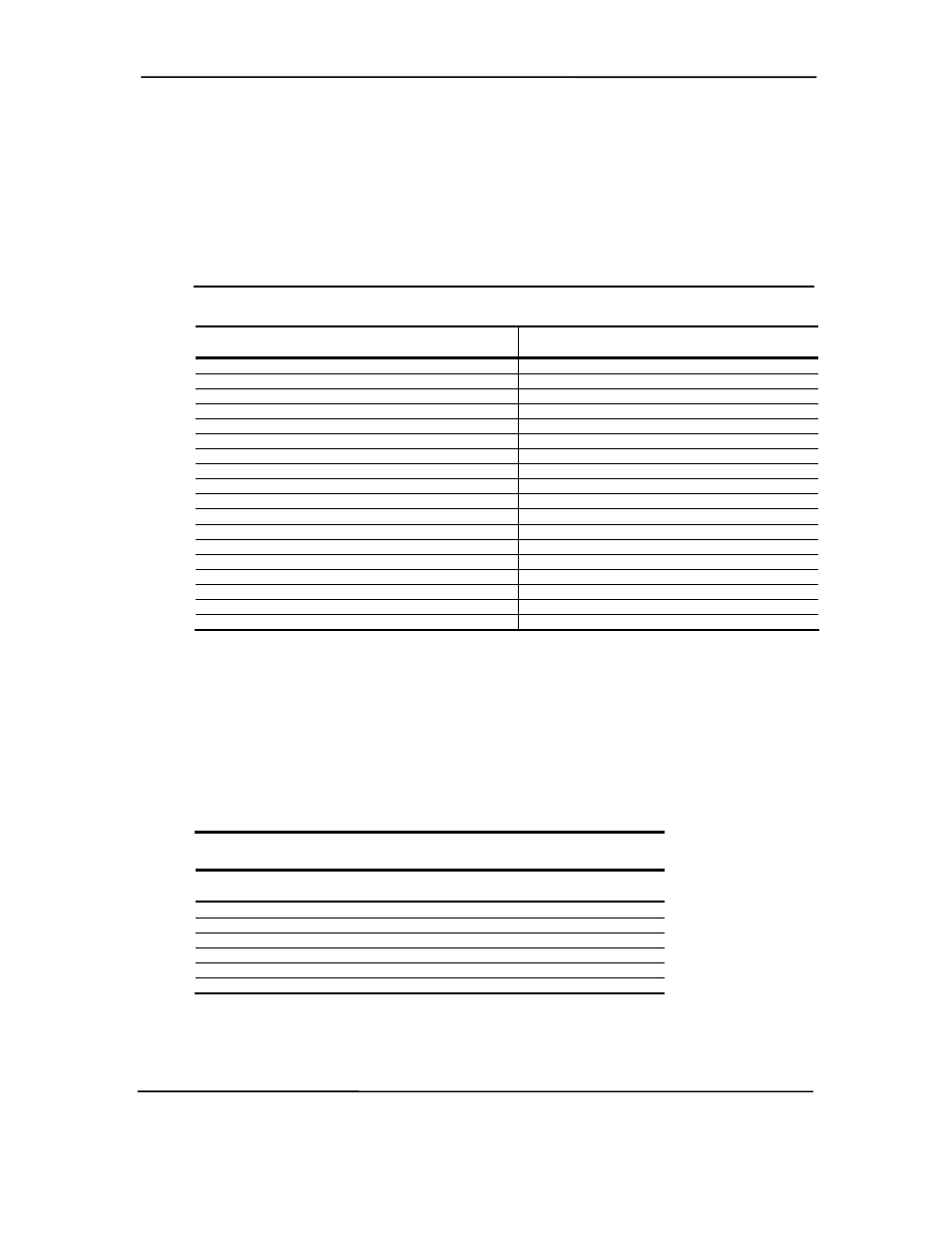

The IDE controller is configured as a PCI device with bus mastering capability. The PCI

configuration registers for the IDE controller function (PCI device #9, function #0) are listed in

Table 5-1.

Table 5–1. IDE PCI Configuration Registers

Table 5-1.

IDE PCI Configuration Registers (MCP, Device 9/Function 0)

PCI Conf.

Addr.

Register

Reset

Value

PCI Conf.

Addr.

Register

Reset

Value

00, 01h

Vender ID

10DEh

3Ch

Interrupt Line

00h

02, 03h

Device ID

[1]

3Dh

Interrupt Pin

01h

04, 05h

PCI Command

0000h

3Eh

Minimum Grant

03h

06-07h

PCI Status

00B0h

3Fh

Maximum Latency

01h

08h

Revision ID

A1h

40h

Write SS Vendor ID

0000h

09 – 0Bh

Class Code

01018Ah

42h

Write SS ID

0000h

0Ch

Cache Line Size

00h

44h

Power Mgmt. Config.

01h

0Dh

Master Latency Timer

00h

45h

Next Item Pointer

00h

0Eh

Header Type

00h

46h

Power Mgmt. Capabilities

E802h

0Fh

BIST

00h

48h

Power Mgmt. Cntrl./Sts.

0000h

10 – 13h

Pri. Cmd. I/O Base Addr.

1d

4Bh

Power Mgmt. Data

00h

14 – 17h

Pri. Cntrl. I/O Base Addr.

1d

50h

IDE Config.

0000h

18 – 1Bh

Sec. CMD I/O Base Addr.

1d

58, 59h

IDE Timing

A8A8h

1C – 1Fh

Sec. Cntrl. I/O Base Addr.

1d

5A, 5Bh

IDE Timing

A8A8h

20h

Bus Mstr. I/O Base Addr.

1d

5Ch

IDE Cycle & Addr. Timing

00FFh

2Ch

Subsystem Vendor ID

0000h

5Dh

IDD Cycle & Addr. Timing

FFFFh

2Eh

Subsystem ID

0000h

60h

UDMA Mode Selection

0s

34h Capabilities

Pointer 44h

- -

-

NOTES:

[1] D315 = 01BCh,

d325 = 0065h

5.2.1.2 IDE Bus Master Control Registers

The IDE interface can perform PCI bus master operations using the registers listed in Table 5-2.

These registers occupy 16 bytes of variable I/O space set by software and indicated by PCI

configuration register 20h in the previous table.

Table 5–2. IDE Bus Master Control Registers

Table 5-2.

IDE Bus Master Control Registers

I/O Addr.

Offset

Size

(Bytes)

Register

Default

Value

00h

1

Bus Master IDE Command (Primary)

00h

02h

1

Bus Master IDE Status (Primary)

00h

04h

4

Bus Master IDE Descriptor Pointer (Pri.)

0000 0000h

08h

1

Bus Master IDE Command (Secondary)

00h

0Ah

2

Bus Master IDE Status (Secondary)

00h

0Ch

4

Bus Master IDE Descriptor Pointer (Sec.)

0000 0000h

NOTE:

Unspecified gaps are reserved, will return indeterminate data, and should not be written to.

5-2 Compaq D315 and hp d325 Personal Computers

Featuring the AMD Athlon XP Processor

Second Edition – April 2003