HP D315 User Manual

Page 55

Technical Reference Guide

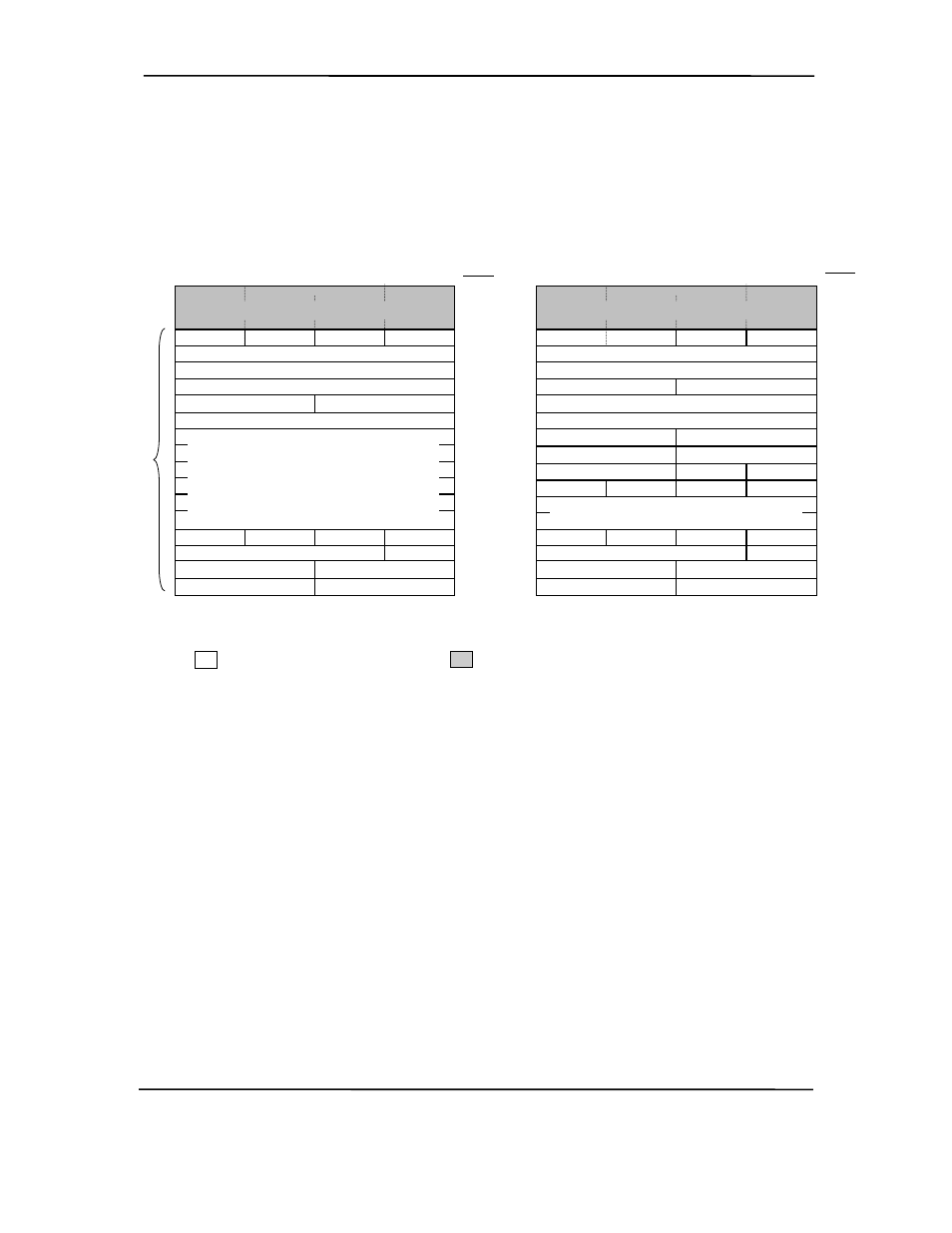

The register index (CF8h, bits <7..2>) identifies the 32-bit location within the configuration space

of the PCI device to be accessed. All PCI devices can contain up to 256 bytes of configuration

data (Figure 4-3), of which the first 64 bytes comprise the configuration space header.

Base Address Registers

10h

Memory Limit

Memory Base

24h

3Ch

40h

38h

18h

20h

1Ch

FCh

2Ch

28h

30h

34h

08h

0Ch

04h

Register

Index

00h

Sub. Bus #

2

nd

Lat.Tmr

Secondary Status

Sec. Bus #

I/O Limit

Pri. Bus #

I/O Base

BIST

Lat. Timer

Device-Specific Area

Prefetch. Mem. Limit

Prefetch. Mem. Base

Prefetchable Base Upper 32 Bits

Expansion ROM Base Address

Bridge Control

Int. Pin

Int. Line

Reserved

Prefetchable Limit Upper 32 Bits

I

/O Limit Upper 16 Bits

I/O Base Upper 16 Bits

Device ID

Vendor ID

0

7

8

15

16

24 23

31

Command

Revision ID

Line Size

Class Code

Hdr. Type

Status

Not required

00h

Register

Index

Base Address Registers

BIST

Min. Lat.

Int. Line

Lat. Timer

Device-Specific Area

Card Bus CIS Pointer

Reserved

Min. GNT

Int. Pin

Reserved

Expansion ROM Base Address

Subsystem ID

Subsystem Vendor ID

Device ID

Status

Hdr. Type

Class Code

Vendor ID

0

7

8

15

16

23

24

31

Command

Revision ID

Line Size

3Ch

40h

38h

FCh

2Ch

28h

30h

34h

04h

08h

0Ch

10h

Configuration

Space

Header

PCI Configuration Space Type 1

PCI Configuration Space Type 0

Data required by PCI protocol

Figure 4-3. PCI Configuration Space Mapping

Each PCI device is identified with a vendor ID (assigned to the vendor by the PCI Special Interest

Group) and a device ID (assigned by the vendor). The device and vendor IDs for the devices on

the system board are listed in Table 4-2 (NOTE: only devices that are implemented in these

systems are listed).

Compaq D315 and hp d325 Personal Computers

Featuring the AMD Athlon XP Processor

Second Edition - April 2003

4-5