Pex8605, 9 jtag interface – 5 pins, 10 i²c slave interface signals – 5 pins – Avago Technologies PEX 8605 User Manual

Page 8

PEX8605

© PLX Technology, www.plxtech.com

Page 8 of 13

2 May 2013, version 1.7

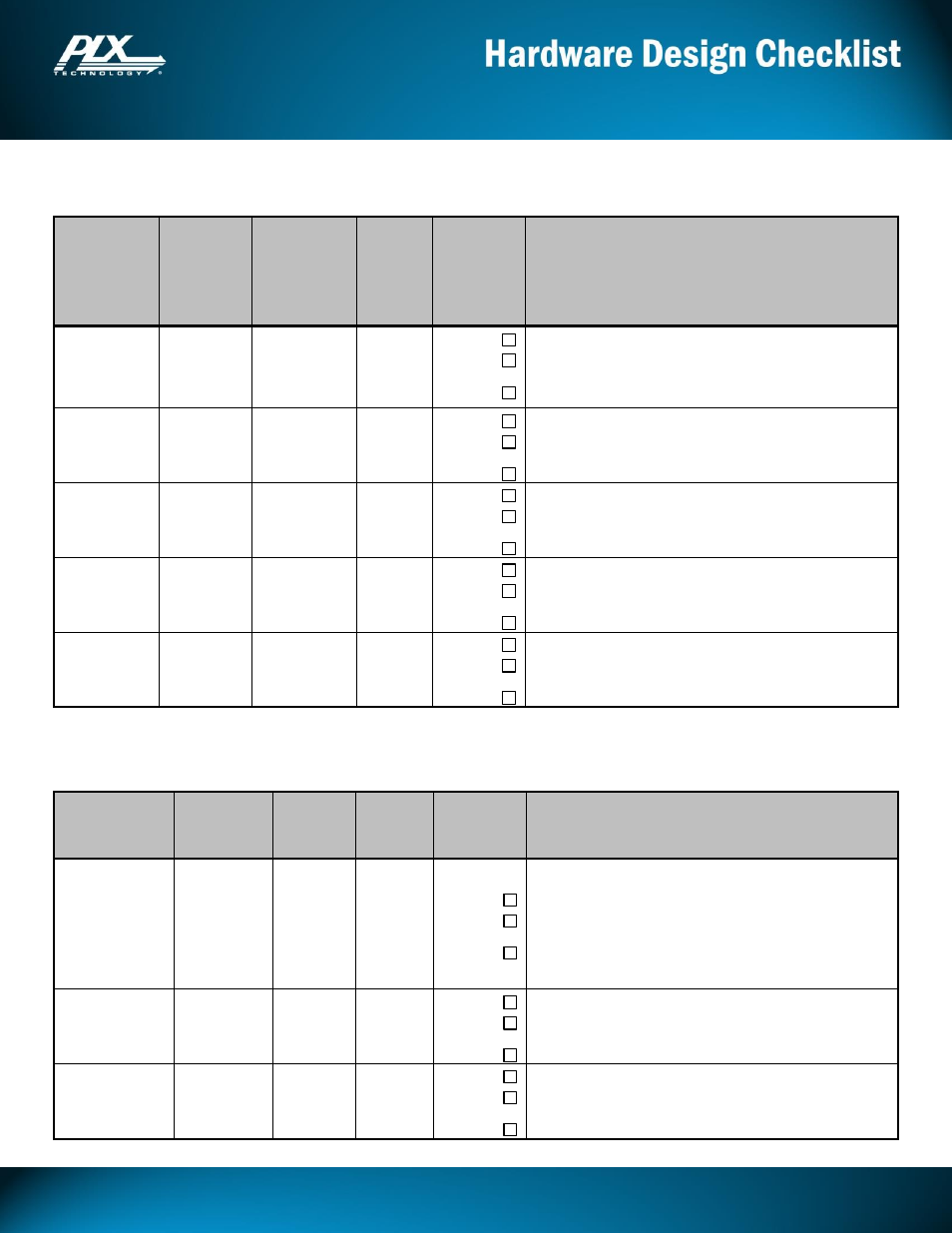

2.9 JTAG Interface – 5 Pins

Signal

Name

Dual-

Row

QFN

Pkg.

Pin #

TQFP

Package

Pin #

Signal

Type

Checked

Recommendations

JTAG_TCK

A48

94

I

PU

YES

NO

UNKNOWN

JTAG Test Clock Input

Frequency can be from 0 to 10 MHz.

This signal is internally pulled up to VDD2.5 through a weak

pull-up resistor. If this pin is connected to external board

circuits, an external pull-up is also recommended.

JTAG_TDI

A47

91

I

PU

YES

NO

UNKNOWN

JTAG Test Data Input

This signal is internally pulled up to VDD2.5 through a weak

pull-up resistor. If this pin is connected to external board

circuits, an external pull-up is also recommended.

JTAG_TDO

B29

65

O

YES

NO

UNKNOWN

JTAG Test Data Output

Serial output from the JTAG TAP Controller test instructions

and data. Can be left open (no connect) if JTAG interface is

not used.

JTAG_TMS

B42

95

I

PU

YES

NO

UNKNOWN

JTAG Test Mode Select

This signal is internally pulled up to VDD2.5 through a weak

pull-up resistor. If this pin is connected to external board

circuits, an external pull-up is also recommended.

JTAG_TRST#

A34

66

I

PU

YES

NO

UNKNOWN

JTAG Test Reset

Pull to GROUND (VSS) through 1.5K ohms for normal

operation

2.10 I²C Slave Interface Signals – 5 Pins

Signal Name Dual-Row

QFN Pkg.

Pin #

TQFP

Package

Pin #

Signal

Type

Checked

Recommendations

I2C_ADDR[2:0]

A41, B36,

A42

80, 81, 82

I

PU

YES

NO

UNKNOWN

I²C Slave Address Bits 2 through 0 (3 Pins)

Used to configure the device address on the I²C Bus. If I²C or

PEX_INTA# output is used, I2C_ADDR[2:0] should be

strapped to a unique address, to avoid address conflict with

any other I²C devices (on the same I²C Bus segment) that have

the upper four bits of their 7-bit I²C Slave address also Set to

1011b. Must be pulled High to VDD25 or Low to VSS (GND)

through external resistors.

I2C_SCL

A45

87

OD

YES

NO

UNKNOWN

I²C Serial Clock

I²C Clock source. This signal must be pulled high to VDD_IO.

Refer to the I2C specification for details.

I2C_SDA0

B39

88

OD

YES

NO

UNKNOWN

I²C Serial Data

Transfers and receives I²C data. This signal must be pulled

high to VDD_IO. Refer to the I2C specification for details.