Pex8605 – Avago Technologies PEX 8605 User Manual

Page 5

PEX8605

© PLX Technology, www.plxtech.com

Page 5 of 13

2 May 2013, version 1.7

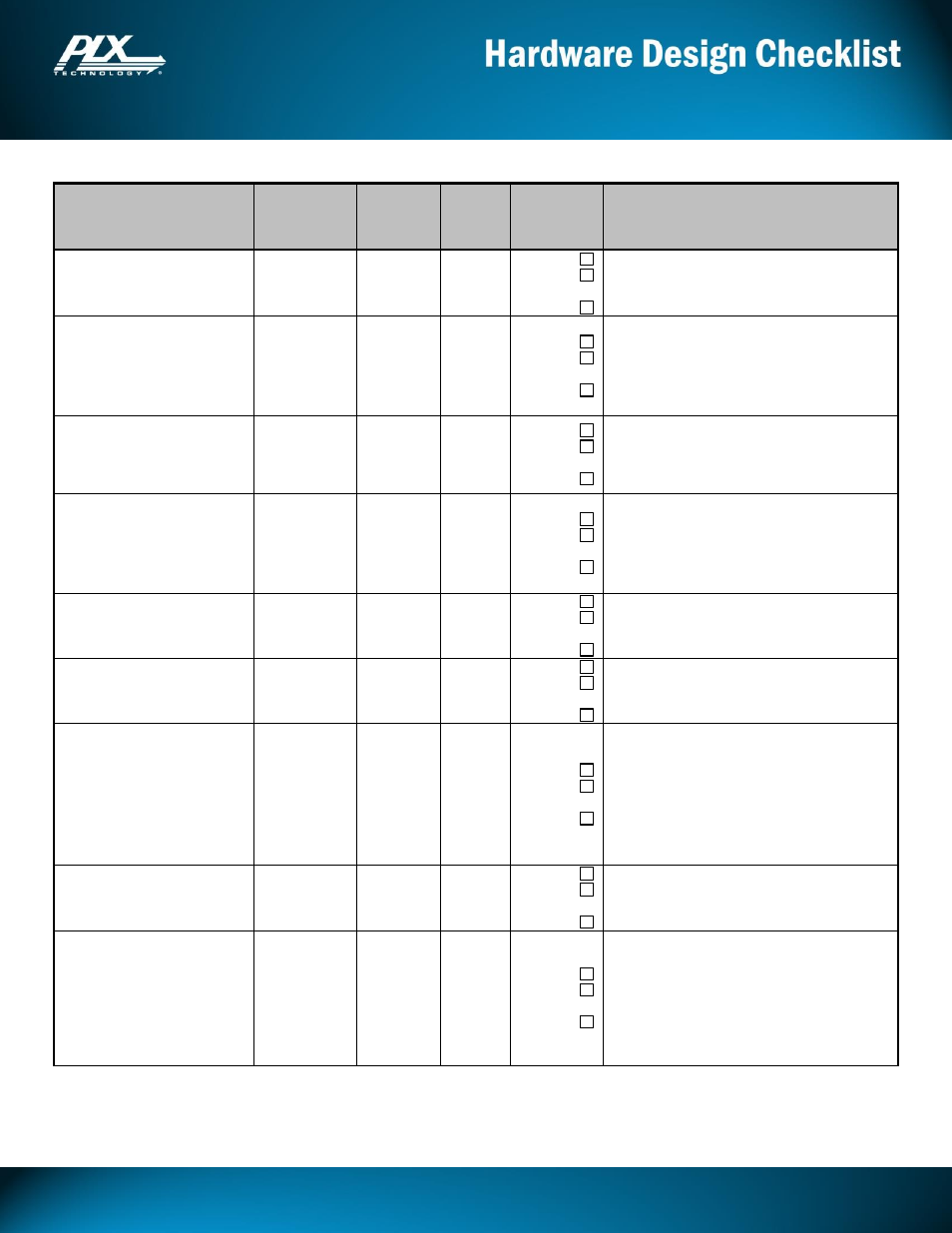

Signal Name

Dual-Row

QFN Pkg.

Pin #

TQFP

Package

Pin #

Signal

Type

Checked

Recommendations

STRAP_LEGACY

C13

97

I

PU

YES

NO

UNKNOWN

Factory Test Only

Do not connect this pin to board circuit traces.

STRAP_PLL_BYPASS#

C12

96

I

PU

YES

NO

UNKNOWN

Factory Test Only

This signal can be left unconnected in normal

applications. If this ball is connected to a board

circuit trace, it must be externally pulled up to

VDD_IO.

STRAP_PORTCFG

B37

83

I

PD

YES

NO

UNKNOWN

Port Configuration Select

L = x1, x1, x1, x1 (Lane 0 is Port 0 up)

H = x2, x1, x1 (Lanes 1:0 form Port 0 up)

STRAP_PROBE_MODE#

C3

27

I

PU

YES

NO

UNKNOWN

Factory Test Only

This signal can be left unconnected in normal

applications. If this ball is connected to a board

circuit trace, it must be externally pulled up to

VDD_IO.

STRAP_RC_MODE

B35

79

I

PD

YES

NO

UNKNOWN

Factory Test Only

Do not connect this pin to board circuit traces.

STRAP_SERDES_MODE_EN#

A39

76

I

PU

YES

NO

UNKNOWN

Factory Test Only

Do not connect this pin to board circuit traces.

STRAP_SMBUS_EN#

B28

62

I

PU

YES

NO

UNKNOWN

System Management Bus Enable

When pulled or tied to Ground, enables SMBus

Slave protocol on the I2C_SCL0 and I2C_SDA0

2-wire bus

When pulled to VDD_IO or unconnected,

enables I

2

C Slave protocol on the I2C_SCL0 and

I2C_SDA0 2-wire bus.

STRAP_SSC_CENTER#

C11

93

I

PU

YES

NO

UNKNOWN

Factory Test Only

Do not connect this pin to board circuit traces.

STRAP_TESTMODE[3:0]

C10, C9, C8,

C7

67, 64, 63,

60

[3,1]: I,

PU

[2,0]: I,

PD

YES

NO

UNKNOWN

Factory Test Only (4 Balls)

Ok to leave these pins unconnected. If external

circuit traces are attached to these pins, they must

be strapped as HLHL.

(STRAP_TESTMODE[3,1] pulled to VDD_IO,

STRAP_TESTMODE[2,0] pulled or tied to

Ground)