Pex8605, Ground pins (20 pins and center pad) – Avago Technologies PEX 8605 User Manual

Page 3

PEX8605

© PLX Technology, www.plxtech.com

Page 3 of 13

2 May 2013, version 1.7

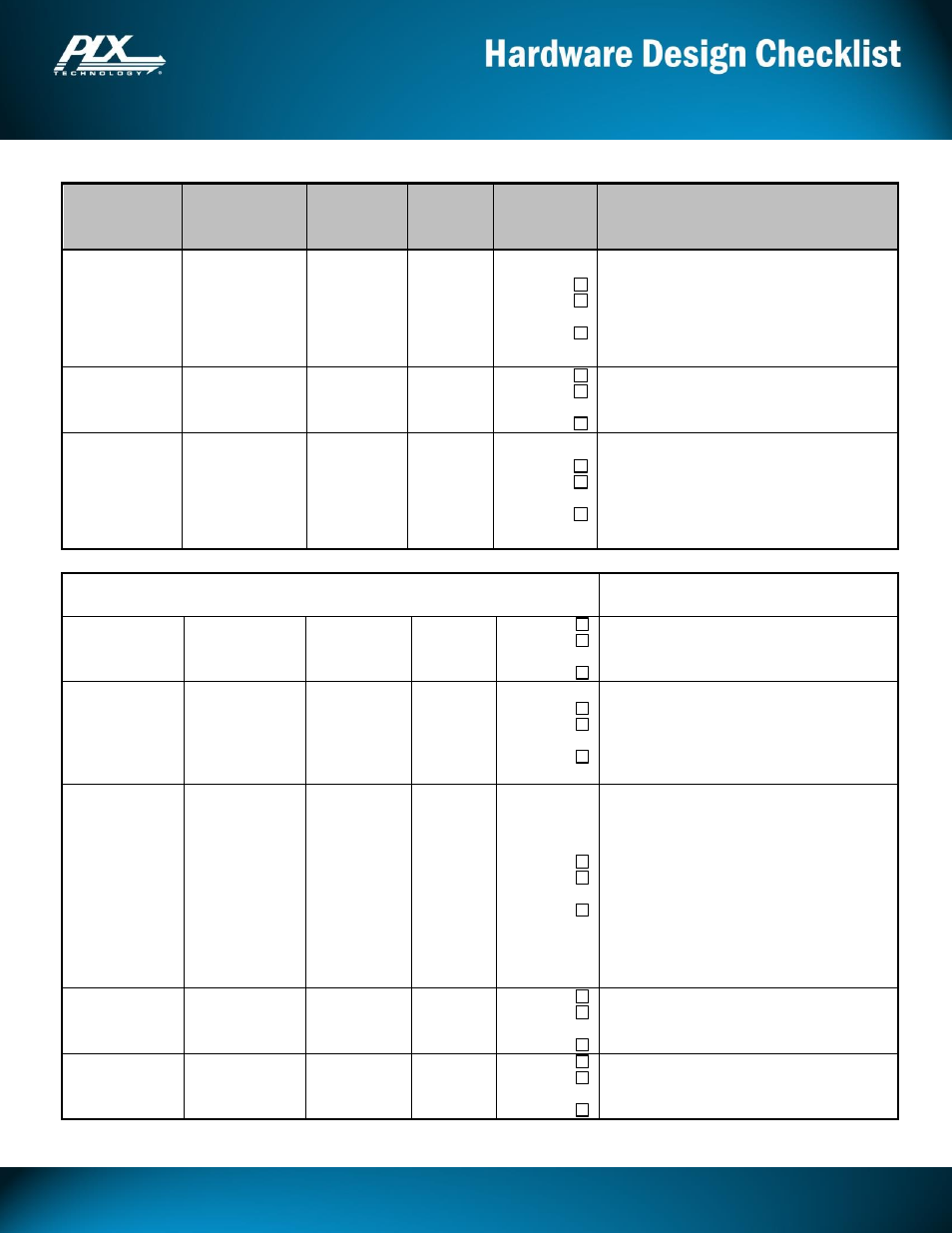

Signal Name Dual-Row

QFN Pkg.

Pin #

TQFP

Package

Pin #

Signal

Type

Checked

Recommendations

PLL_AVDD

A31

58

PLLPWR

YES

NO

UNKNOWN

1.0 V Power for PLL Analog Circuits

This pin supplies power to the internal PLL. As

such it is sensitive to noise, and should be filtered

from the main 1.0V supply (VDD_CORE) to

reduce noise. See the RDK schematic for an

example filter circuit.

VDD_CORE

A29, A37, A46,

A50, B26, B43

54, 57, 72, 89,

98, 99

CPWR

YES

NO

UNKNOWN

1.0 V Power for Core Digital Logic (6 Pins)

Main 1.0 V supply for digital core logic.

VAUX_CORE

A10, A57, B49

15, 16, 112,

113

CPWR

YES

NO

UNKNOWN

1.0 V Auxiliary Core Logic Power Supply

(QFN: 3 Pins, TQFP: 4 pins)

If stand-by power is implemented, this power

supply should be regulated from Vaux (3.3V).

Otherwise, connect these pins to the VDD_CORE

supply.

Ground Pins (20 Pins and Center Pad)

Connect all Ground pins below directly to Ground

(plane).

PLL_AGND

B27

59

GND

YES

NO

UNKNOWN

Connect to Ground

PEX_VSSA_P0

PEX_VSSA_P1

PEX_VSSA_P2

PEX_VSSA_P3

A9

A15

A51

A58

13

25

102

115

GND

YES

NO

UNKNOWN

Connect to Ground (4 Pins)

PEX_VSSD0_P0

PEX_VSSD0_P1

PEX_VSSD0_P2

PEX_VSSD0_P3

PEX_VSSD1_P0

PEX_VSSD1_P1

PEX_VSSD1_P2

PEX_VSSD1_P3

B5

A12

A54

B53

B4

B9

B48

B54

8

20

107

120

5

17

110

123

GND

YES

NO

UNKNOWN

Connect to Ground (8 Pins)

VSS

A25, A32, A56,

A63, B17, B18,

B20

37, 40, 44, 47,

61, 111, 124

GND

YES

NO

UNKNOWN

Ground (7 Pins)

Connect to Ground

GROUND (VSS)

CENTER_PAD

CENTER_PAD

GND

YES

NO

UNKNOWN

Connect to Ground

See package drawing for pad dimensions.