Operation, Use during development – Remote Processing RPC-220 User Manual

Page 32

WATCHDOG TIMER

SECTION 9

Page 9-1

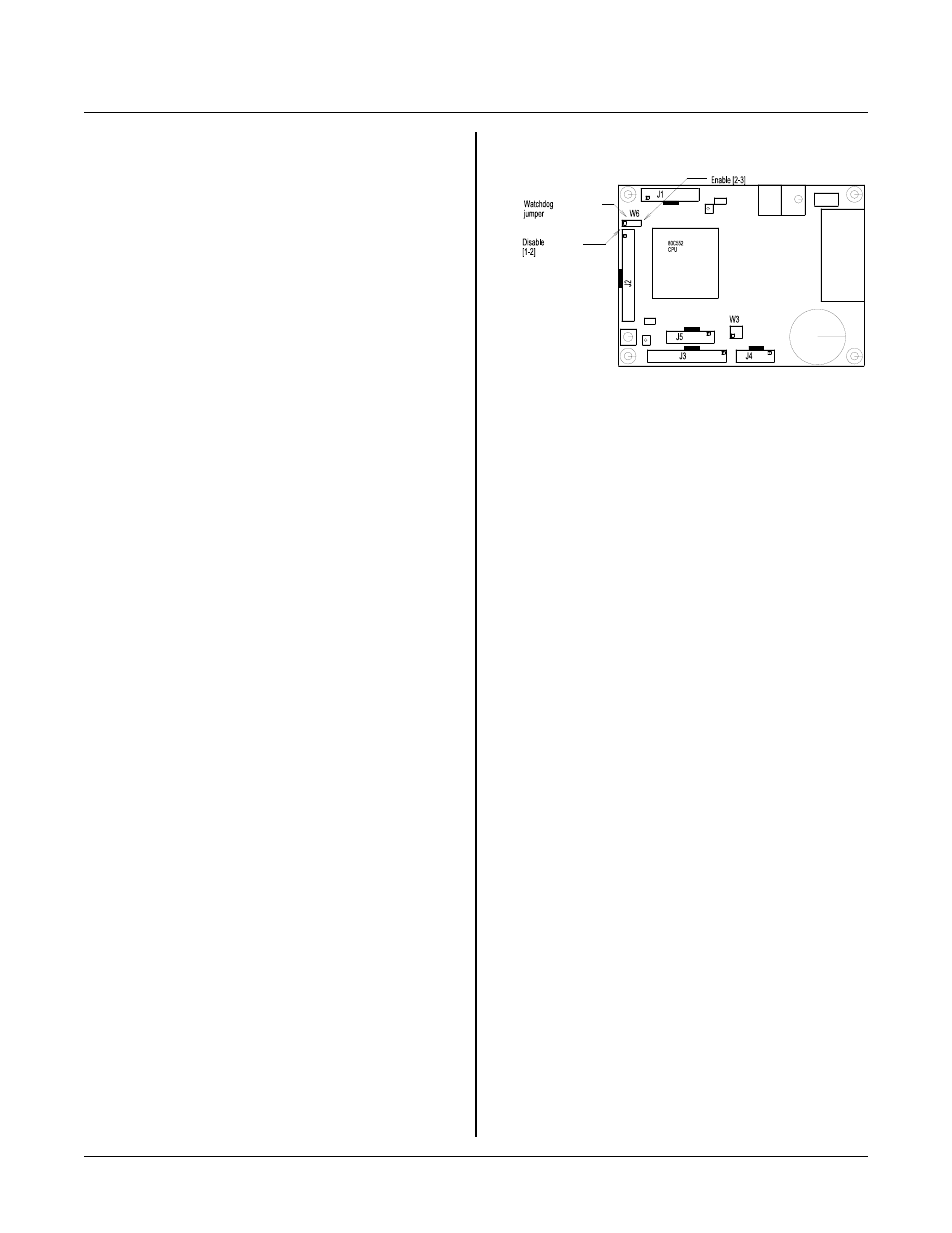

Figure 9-1 Watchdog Jum per Location

WATCHDOG TIMER

S E C T IO N 9

A watch dog timer r esets the CPU if it enters erroneous

process or states or "loop fo rever " code . T he timer is

reloaded in periods that are shorter than the watchdog

interval. The timer is built into the CPU and is enabled

or disabled by jumper W6.

OPERATION

When the w atchdog timer is ena bled and overflow s, a

short reset pulse, internal to the CPU , is generated. A

short output pulse is also generated but does not have

any effect on the reset signal at J2 or J3.

Inform ation about the w atchdog star ts on page 3-48 0 in

the 8X0C552OV. PDF file.

The tim er consists o f an 8 bit timer and an 11 bit

prescaler. The 8 bit timer is loaded to prevent a reset

pulse. Watchdog timer interval is determined by the

following formula:

interval = 1.111 m s * timer_value

The w atchdog ser vice routin e is very sh ort:

watchdog:

ORL PCON,#10H

;set condition

MOV T3,timer_value

;load with

;interval

RET

This should be in assembly language even when using C

to prevent it from wrongly ma nipulating PCON. The

address of T3 is 0xff.

USE DURING DEVELOPMENT

The watchdog jumper W 6 is set to [1-2] to disable it. If

you want to enable it for debugging purposes, you can

set the jumper to enable (W6[2-3]) while your program

is running. If a watchdog crash happens, the program

will reset and the monitor program

When y our pr ogram is in flash, you can set W 6[2-3] all

of the time.

On power up or reset, the watchdog timer is reset to 0,

which is a timeout interval of 283 ms. This is enough

t im e fo r ba si c s ys te m in it ia li za ti on (m e m or y an d I/ O

states). If you are perform ing extensive initialization

(such as clearing 512K of RAM) then you should put the

w a tc h do g r ou ti ne a s p a r t o f th e pr o g ra m .