Sundance SMT351T User Manual

Page 18

SMT351T User Guide

Page 18 of 37

Last Edited: 04/09/2009 11:26:00

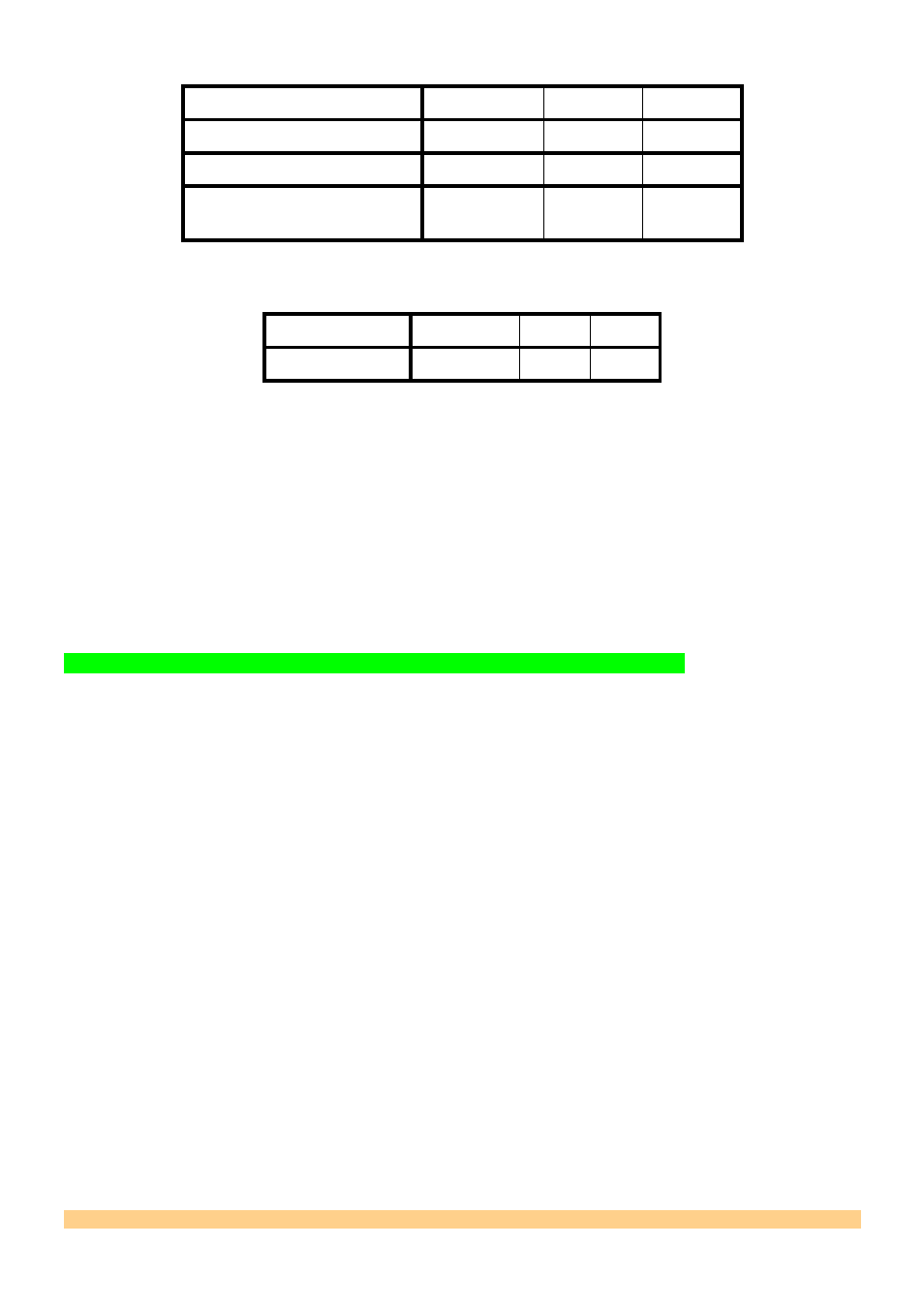

Table 2: DIP switch SW1 position for the selection of the configuration bitstream source

Table 3: DIP switch SW1 position for the selection of the Flash erase & program operations.

The Flash erase & program operations are operated by the CPLD.

Commands are provided via Comport3 from an application running on a Host or DSP.

On the Host, this application is the SMT6002, please ask Sundance as it is not yet available

under the Sundance Wizzard.

Status information from the Flash is given over Comport3 as well.

4.2.13 Available clocks

Two onboard clocks:

• 50mhz LVTTL oscillator. Used by the CPLD and connected to the FPGA.

• 125mhz LVDS oscillator. Connected to the FPGA. Used to clock the MGTs.

An external clock can be input into the Virtex 5 FPGA via the SLB connector.

Sundance applies this scheme for ADC/DAC mezzanines.

SW1 pos 3,2, 1

JPC3

JPC2

JPC1

C3P OFF

OFF

OFF

Flash boots from address 0

OFF

OFF

ON

Flash boots from address

0x800000

OFF ON ON

SW1 pos 3,2, 1

JPC3

JPC2

JPC1

Flash accesses

ON

OFF

OFF