Comtech EF Data DMD1050 User Manual

Page 29

DMD1050 Satellite Modem Board

Theory of Operation

MN-DMD1050

3–3

Revision 9

FPGA. There is no limit to the number of digital logic configurations available to the FPGA,

aside from the amount of Flash memory available to the system microprocessor for storage of

configuration files.

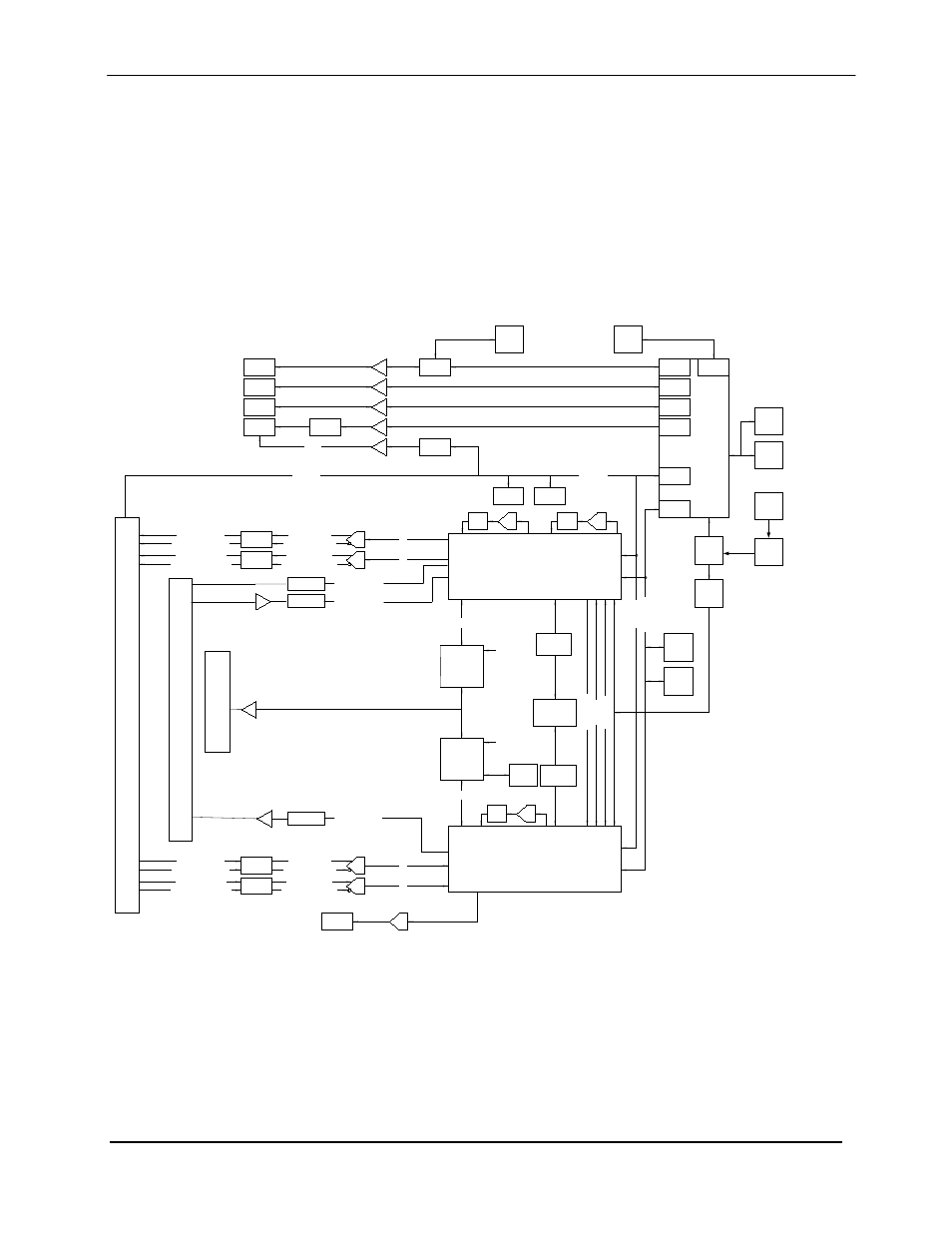

The DMD1050 Baseband Processing Printed Circuit Card provides a flexible architecture that

allows many different modes of terrestrial and satellite framing, various FEC options, digital

voice processing, and several different modulation/demodulation formats. Also included on the

Baseband Printed Circuit Card is a MIL-188-114A/RS-422 synchronous interfaces and a two port

10/100 Ethernet Bridge interface.

A block diagram of the Baseband Processing Card is shown in Figure 3-3.

Figure 3-3. DMD1050 Baseband Processing Card Block Diagram

Battery

Xtal

uProcessor

PCMCIA

Controller

SCC2

SMC2

SCC3

GPIO

uProc

Bus

SPI

40

MHz

x2

Compact

Flash

Demodulator

FPGA

SDRAM

2 x

Boot

Flash

8 Mbx8

256 Mbx16

25 MHz

Xtal

Ethernet

PHY

Relays

Fault

(DB9)

RLLP

Terminal

Ethernet

DAC

AGC

Modulator

FPGA

SCT

/SCTE

Rx SAT

Loopback

80 MHz

uProc Bus

SPI Bus

I/Q

TP

2 x

r2r

Q

I

ADC

ADC

Analog I Filter

Analog I Inv Filter

Analog Q Inv Filter

Analog Q Filter

Alias

Filter

Alias

Filter

Analog I Unfilter

Analog I Inv Unfilter

Analog Q Unfilter

Analog Q Inv Unfilter

DMD

1050

IF Board Connector

(40

-Pin Header

)

I

Q

Analog Q Inv Unfilter

Analog Q Unfilter

Analog I Inv Unfilter

Analog I Unfilter

Analog I Filter

Analog I Inv Filter

Analog Q Filter

Analog Q Inv Filter

Alias

Filter

Alias

Filter

ADC

ADC

DB

-25

Sync Data

(RS

-422

,

MIL

-STD

-188

-114

A

)

&

Ethernet

10

Base

-T

TPC Codec

ADC

Serial

EEPROM

SPI Bus

SPI Bus

Terrestrial Data

LPF

DAC

Tx

Clk

SCT

LPF

R2R

SCT

R2R

LPF

Insert DSP

Mem Space DMA

Drop DSP

Mem Space DMA

Buf

SRAM

40 MHz

40 MHz

Async

(DB

-9

)

Buffers

Terrestrial Data

Buffers

Terrestrial Data

Buffers

10 Mhz

OCXO

PLL

Buffers

Buffers