Specifying your flash programmer settings, Specifying your flash programmer settings –2, Figure 2–1 – Altera Nios II User Manual

Page 10

2–2

Chapter 2: Using the Flash Programmer GUI

Starting the Flash Programmer GUI

Nios II Flash Programmer User Guide

© March 2014

Altera Corporation

Specifying your Flash Programmer Settings

Before writing data to flash memory, you must determine the flash programmer

settings.

To create a new set of flash programmer settings, complete the following steps:

1. On the File menu, click New. The New Flash Programmer Settings File dialog

box appears.

2. Select Get flash programmer system details from BSP Settings File or Get flash

programmer system details from SOPC Information File

.

3. Browse to locate your BSP Settings File (.bsp) or SOPC Information File

(.sopcinfo).

4. For a multiprocessor system, select the processor. If you specify a .bsp file, the

processor is already specified.

5. Click OK. The New Flash Programmer Settings File dialog box closes and the

Nios II Flash Programmer GUI populates with your processor selection, if

relevant, and the information from the .bsp or .sopcinfo file.

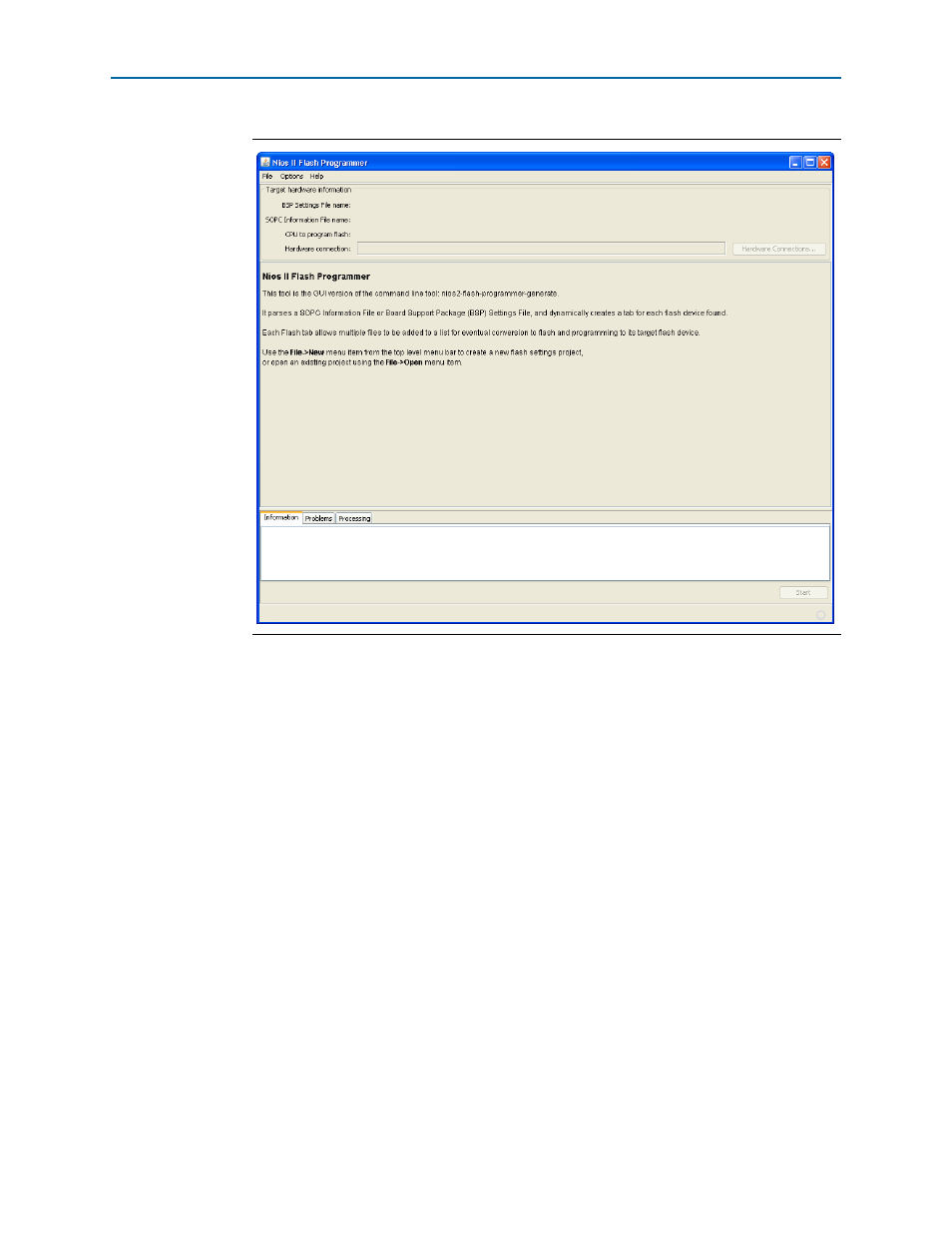

Figure 2–1. Flash Programmer Dialog Box