Building blocks of a pll – Altera Phase-Locked Loop User Manual

Page 8

(lock) on the frequency of the input or reference signal. The synchronization or negative feedback loop of

the system forces the PLL to be phase-locked.

You can configure PLLs as frequency multipliers, dividers, demodulators, tracking generators, or clock

recovery circuits. You can use PLLs to generate stable frequencies, recover signals from a noisy communi‐

cation channel, or distribute clock signals throughout your design.

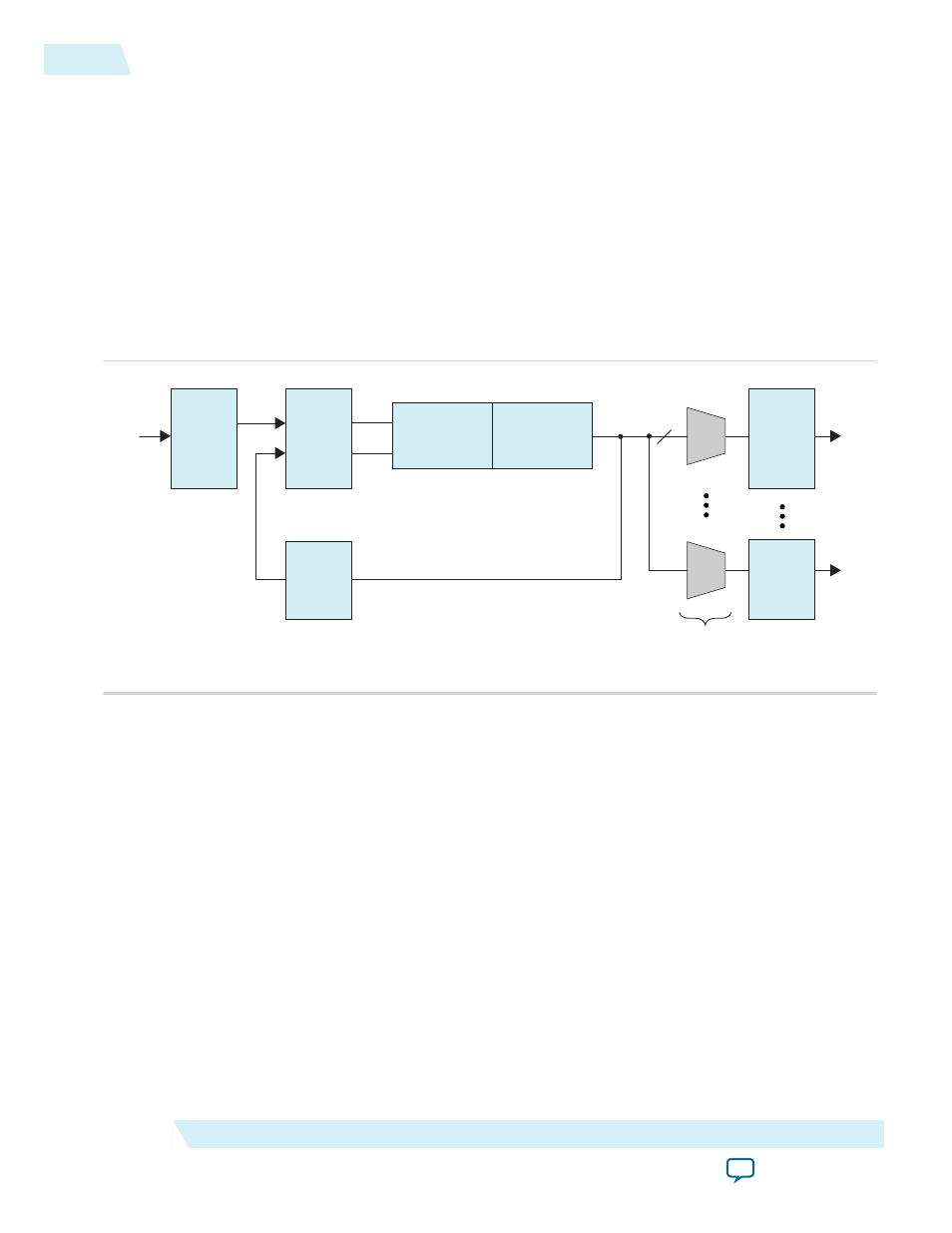

Building Blocks of a PLL

The main blocks of the PLL are the phase frequency detector (PFD), charge pump, loop filter, VCO, and

counters, such as a feedback counter (

M

), a pre-scale counter (

N

), and post-scale counters (

C

). The PLL

architecture depends on the device you use in your design.

Figure 1: Typical PLL Architecture

F

IN

F

FB

F

REF

Up

Down

F

VCO

Pre-scale

Counter

(N)

# of

output

clocks

Phase

Frequency

Detector

(PFD)

Charge Pump

Loop Filter

and VCO

Feedback

Counter

(M)

Post-scale

Counter

(C)

Post-scale

Counter

(C)

VCO Phase Selection

at Each PLL Output Port

The following terms are commonly used to describe the behavior of a PLL:

• PLL lock time—also known as the PLL acquisition time. PLL lock time is the time for the PLL to attain

the target frequency and phase relationship after power-up, after a programmed output frequency

change, or after a PLL reset.

Note: Simulation software does not model a realistic PLL lock time. Simulation shows an unrealisti‐

cally fast lock time. For the actual lock time specification, refer to the device datasheet.

• PLL resolution—the minimum frequency increment value of a PLL VCO. The number of bits in the

M

and

N

counters determine the PLL resolution value.

• PLL sample rate—the F

REF

sampling frequency required to perform the phase and frequency

correction in the PLL. The PLL sample rate is f

REF

/

N

.

Related Information

Provides more information about the PLL building blocks.

8

Building Blocks of a PLL

UG-01087

2015.05.04

Altera Corporation

Altera Phase-Locked Loop (Altera PLL) IP Core User Guide