Cos interrupt control registers – ADLINK PCI-7442 User Manual

Page 46

34

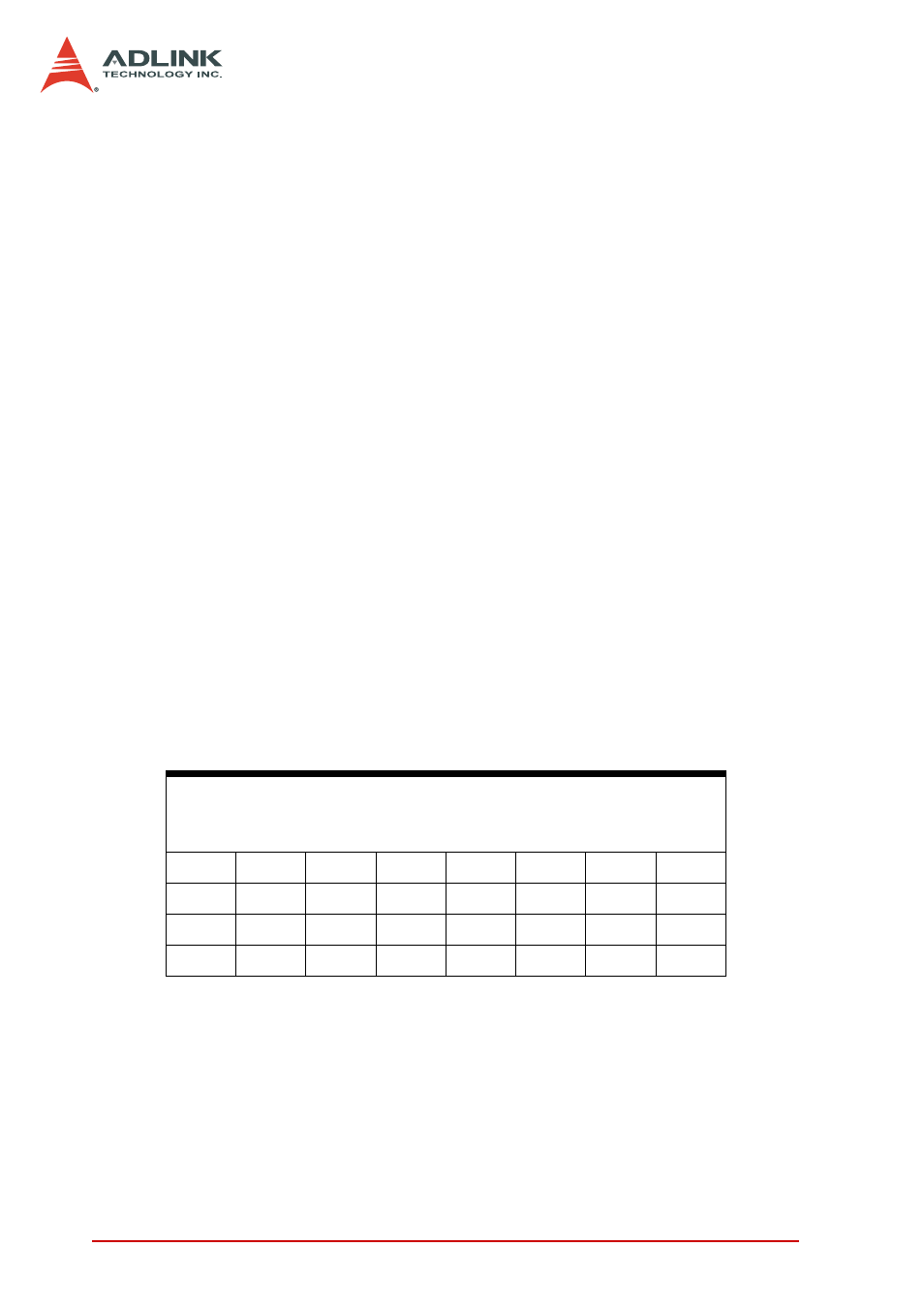

Register Format

COS Interrupt Control Registers

There are two different interrupt modes in PCI-7442. Both interrupt

modes are disabled by default. You can write the registers listed

below to enable the interrupt. In the first mode, users enable the

COS (Change of State) interrupt function to monitor the status of

enabled input channels and whenever the status change from 0 to

1 or 1 to 0. In the second mode, you can enable the Watchdog

Timer (WDT) Counter. The interrupt asserts when the WDT Coun-

ter counts to zero. After processing the interrupt request event,

you have to clear the interrupt request in order to handle another

interrupt request. Take note that it takes time for a system to clear

the interrupt. That is, any COS interrupt or WDT interrupt that

came before the previous interrupt and has not cleared will be

ignored. To clear the interrupt request, write 1 to the correspond-

ing bit (CLRn). The WDT INT control registers are shown below.

The COS interrupt is enabled by two registers. Because the 64

digital inputs are divided into two 32-bit onboard buses, every 32

inputs are connected to a CPLD. When you enable COS interrupt

EA0 (BASE+0x06h), the first CPLD (CPLD0) generates an inter-

rupt signal while the first 32 inputs IDI[31..0] have state change.

When you enable COS interrupt EA1 (BASE+0x46h), the second

CPLD (CPLD1) generates an interrupt signal while the second 32

inputs IDI[63..32] have state change.

Address: BASE+0x06h

Reset Value: 0x0000h

Read/Write: W

--

--

--

--

--

--

--

CLR0

Bit7

Bit6

Bit5

Bit4

Bit3

Bit2

Bit1

Bit0

--

--

--

--

--

--

--

EA0

Bit15

Bit14

Bit13

Bit12

Bit11

Bit10

Bit9

Bit8

Bit15 - 9

Not used

Bit7 - 1

Not used

Bit0

CLR0: COS 0 interrupt clear

1: Clear; 0: No effect

Bit8

EA0: COS 0 interrupt enable/disable

1: Enabled; 0: Disabled