Capacitance, Thermal resistance – Cypress CY7C1012DV33 User Manual

Page 4

CY7C1012DV33

Document Number: 38-05610 Rev. *D

Page 4 of 11

Capacitance

Tested initially and after any design or process changes that may affect these parameters

.

Parameter

Description

Test Conditions

Max

Unit

C

IN

Input Capacitance

T

A

= 25

°C, f = 1 MHz, V

CC

= 3.3V

8

pF

C

OUT

I/O Capacitance

10

pF

Thermal Resistance

Tested initially and after any design or process changes that may affect these parameters.

Parameter

Description

Test Conditions

119-Ball

PBGA

Unit

Θ

JA

Thermal Resistance

(junction to ambient)

Still air, soldered on a 3 × 4.5 inch,

four layer printed circuit board

20.31

°C/W

Θ

JC

Thermal Resistance

(junction to case)

8.35

°C/W

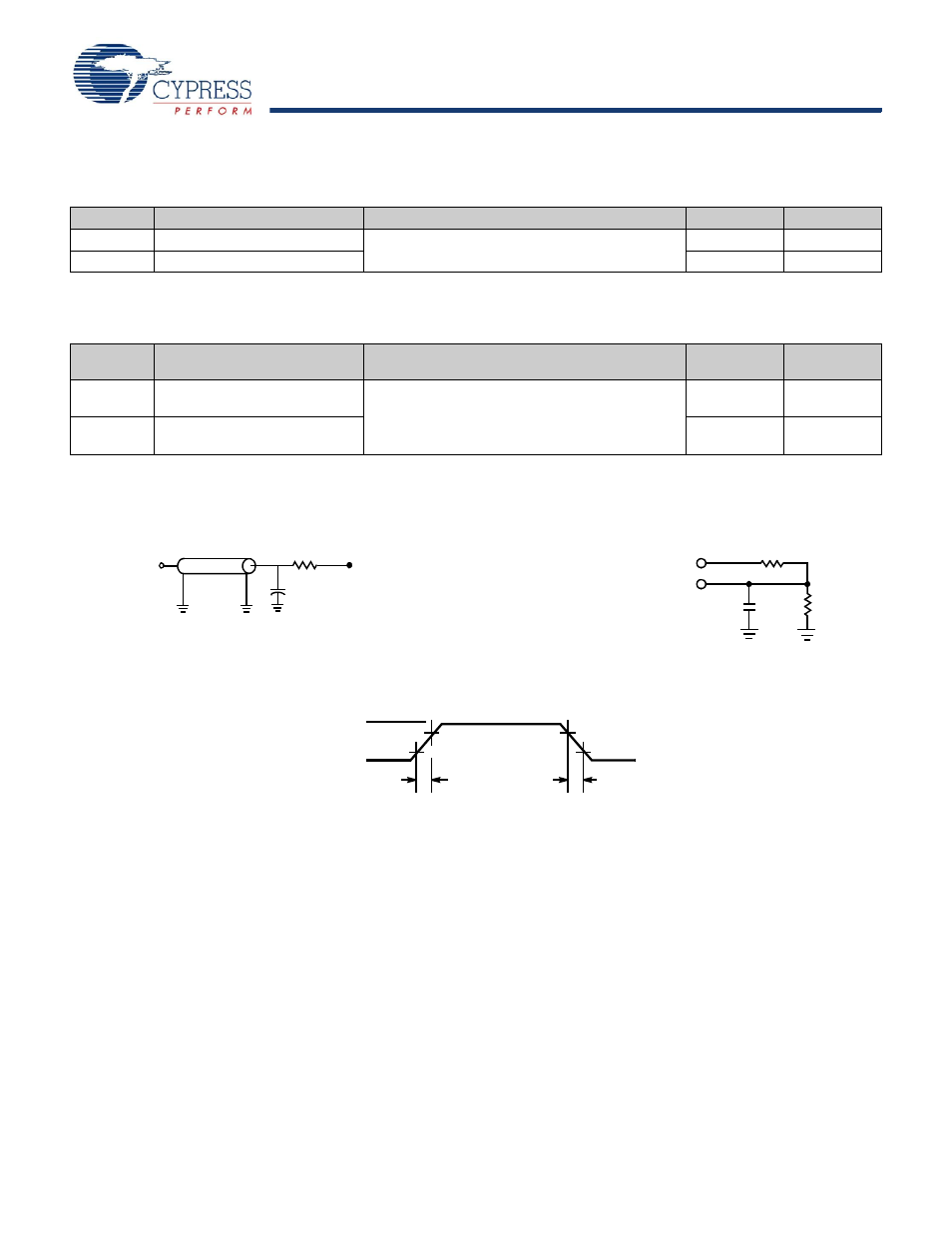

Figure 2. AC Test Loads and Waveforms

90%

10%

3.0V

GND

90%

10%

All input pulses

3.3V

OUTPUT

5 pF*

(a)

(b)

R1 317

Ω

R2

351

Ω

Fall Time:> 1V/ns

(c)

OUTPUT

50

Ω

Z0= 50Ω

V

TH

= 1.5V

30 pF*

*

Capacitive Load consists of all

components of the test environment

Rise Time > 1V/ns

*Including jig

and scope

Note

4. Valid SRAM operation does not occur until the power supplies have reached the minimum operating V

DD

(3.0V). 100

μs (t

power

) after reaching the minimum operating

V

DD

, normal SRAM operation begins including reduction in V

DD

to the data retention (V

CCDR

, 2.0V) voltage.