7 hardware design information, 1 board schematics, Hardware design information – Maxim Integrated 78M6610+LMU Evaluation Kit User Manual

Page 24: Board schematics, S2 s0

78M6610+LMU Evaluation Kit User Manual

24

Rev 1

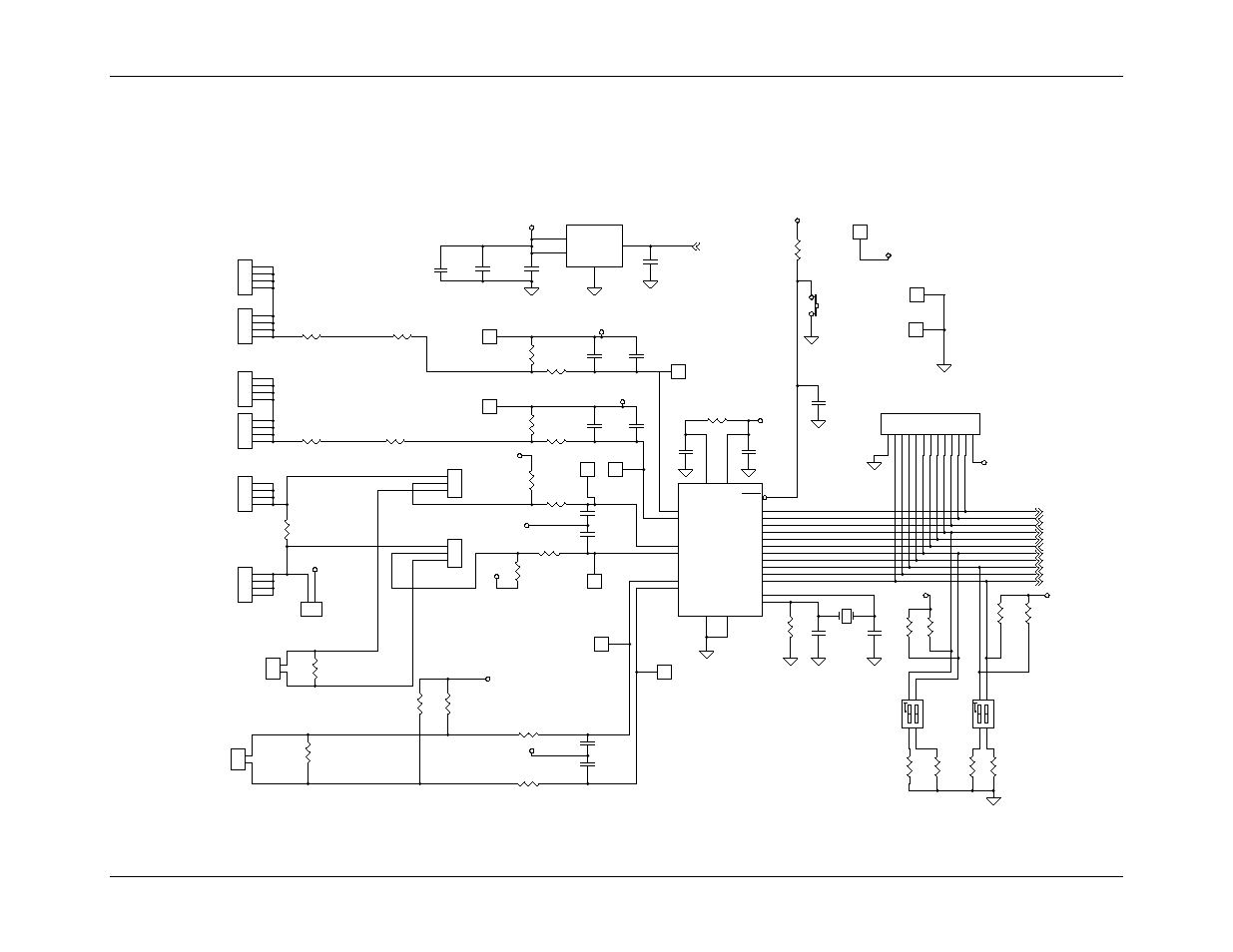

7 Hardware Design Information

This section includes the schematics, bill of materials, and PCB layouts for the 78M6610+LMU EV board.

7.1 Board Schematics

C7

0.1uF

0603

J10

1

2

R32

750 1%

0603

J3

CON1

1

C12

1000pF

0603

J8

CON4

1

2

3

4

R12

0

0603

J14

1

2

R79

1K

J13

CON1

1

R73

10K

R18

0

0603

J32

CON1

1

R9

1M 0.1%

1206W

U1

78M6610+LMU

TQFN24

V3

P3

A

21

MP10 16

A0

19

XOUT 10

GNDA

2

A1

20

MP6/ADDR1 5

A3

23

A4

24

XIN 9

A2

22

SSB/DIR/SCL 6

SPCK/ADDR0 14

MP4 7

IFC1 17

RESET 18

SDI/RX/SDAo 13

A5

1

MP7 4

IFC0 3

GNDD

11

MP0 15

SDO/TX/SDAi 12

V3

P3

D

8

J7

CON13

1

2

3

4

5

6

7

8

9

10

11

12

13

R26

0.004 1% 2.5W

2512P

R71

10K

C3

10uF

0805

SW4

SW DIP-2

J35

CON1

1

J11

CON4

1

2

3

4

J4

CON4

1

2

3

4

J36

CON1

1

R70

Rburden

R11

750 0.1%

0603

C8

0.1uF

0603

VR1

+3.3V 500mA

511-LD1117S33C

SOT223

VOUT

2

VIN

3

TAB

4

GND

1

J15

CON4

1

2

3

4

J34

CON1

1

R75

10K

R3

10K

0603

R33

10K

0603

J26

CON1

1

R69

Rburden

C13

1000pF

0603

Y1

20.00MHz

1

2

R80

1K

C18

18pF

0603

R29

750 1%

0603

R16

1M 0.1%

1206W

J37

CON1

1

J25

CON1

1

R19

0

0603

R10

1M 0.1%

1206W

C5

NC

0603

J2

CON4

1

2

3

4

C9

1000pF

0603

C10

1000pF

0603

J33

CON1

1

C1

0.1uF

0603

C2

0.1uF

0603

C6

NC

0603

R78

1K

R76

0(NC)

C4

1000pF

0603

SW1

J5

CON4

1

2

3

4

J23

CON3

1

2

3

J9

CON2

SIP100P2

1

2

R24

750 1%

0603

R15

750 0.1%

0603

R39

10K

0603

R38

10K

0603

R36

10K

0603

J6

CON1

1

C14

1000pF

0603

SW5

SW DIP-2

J24

CON3

1

2

3

R17

1M 0.1%

1206W

R77

1K

C15

1000pF

0603

C19

18pF

0603

C11

0.1uF

0603

R28

750 1%

0603

R72

10K

GND

GND

GND

V3P3A

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

+5VISO

V3P3

V3P3

V3P3

V3P3A

V3P3A

V3P3

V3P3A

V3P3A

GND

V3P3

V3P3A

V3P3A

V3P3

V3P3

V3P3A

V3P3A

SPCK

SDO

SSB

SDI

MP0

MP4

MP6

MP7

IFC0

MP10

IFC1

+5VISO

S2

S0

MP0

SPCK/ADDR0

SDI/RX/SDAo

SDO/TX/SDAi

SSB/DIR/SCL

MP6/ADDR1

MP7

IFC0

MP10

IFC1

CT2

CT1

GPIO ACCESS

For

int.

OSC

MP

0

SDO

/TX

/SDAi

SDI

/RX

/SDAo

SPCK

/ADDR

0

MP

4

MP4

SSB

/DIR

/SCL

MP

7

IFC

0

MP

6/

ADDR

1

MP

010

IFC

1

MP0

IFCF1

SSB

LINE A IN

LINE B IN

NEUTRAL OUT

NEUTRAL IN

S1

S3

Figure 4: 78M6610+LMU Evaluation Board Electrical Schematic (1 of 4)