Power up sequence in ddr-ii+ sram, Power up sequence, Dll constraints – Cypress CY7C1166V18 User Manual

Page 19: Power up waveforms

CY7C1166V18, CY7C1177V18

CY7C1168V18, CY7C1170V18

Document Number: 001-06620 Rev. *D

Page 19 of 27

Power Up Sequence in DDR-II+ SRAM

DDR-II+ SRAMs must be powered up and initialized in a

predefined manner to prevent undefined operations. During

power up, when the DOFF is tied HIGH, the DLL gets locked after

2048 cycles of stable clock.

Power Up Sequence

■

Apply power with DOFF tied HIGH (all other inputs can be HIGH

or LOW)

❐

Apply V

DD

before V

DDQ

❐

Apply V

DDQ

before V

REF

or at the same time as V

REF

■

Provide stable power and clock (K, K) for 2048 cycles to lock

the DLL.

DLL Constraints

■

DLL uses K clock as its synchronizing input. The input must

have low phase jitter, which is specified as t

KC Var

.

■

The DLL functions at frequencies down to 120 MHz.

■

If the input clock is unstable and the DLL is enabled, then the

DLL may lock onto an incorrect frequency, causing unstable

SRAM behavior. To avoid this, provide 2048 cycles stable clock

to relock to the desired clock frequency.

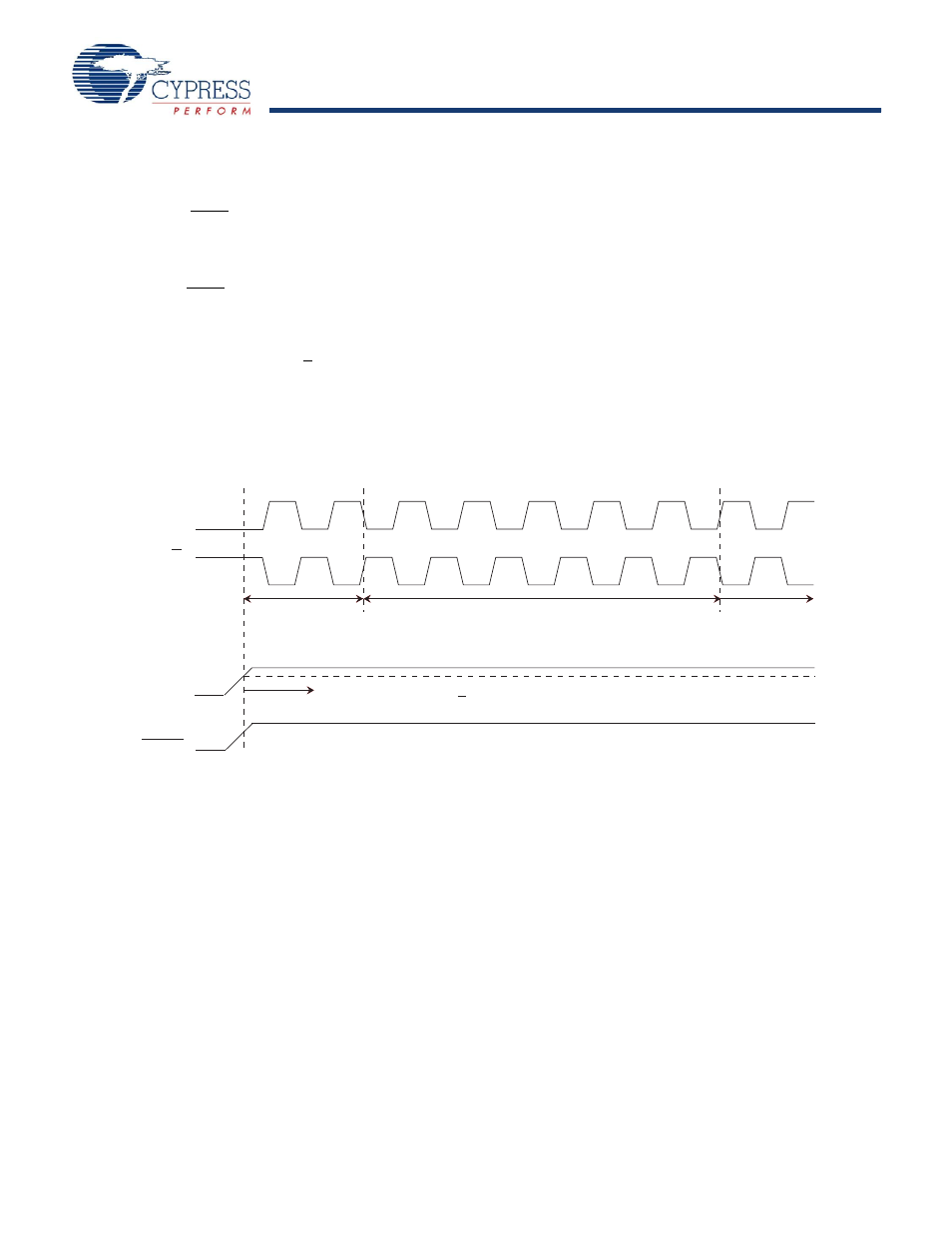

Power Up Waveforms

Figure 5. Power Up Waveforms

K

K

Fix HIGH (tie to VDDQ)

VDD/VDDQ

DOFF

Clock Start (Clock Starts after VDD/VDDQ is Stable)

Unstable Clock

> 2048 Stable Clock

Start Normal

Operation

~ ~

~ ~

VDD/VDDQ Stable (< + 0.1V DC per 50 ns)