Pin configurations product portfolio, Pin definitions, Product v – Cypress CY62128B User Manual

Page 2: Ma) standby, i, Μ a) min. typ, Max. typ, Input a, Address inputs input/output i/o, Chip enable 1, active low. input/control ce, Power supply for the device

CY62128B

MoBL

®

Document #: 38-05300 Rev. *C

Page 2 of 11

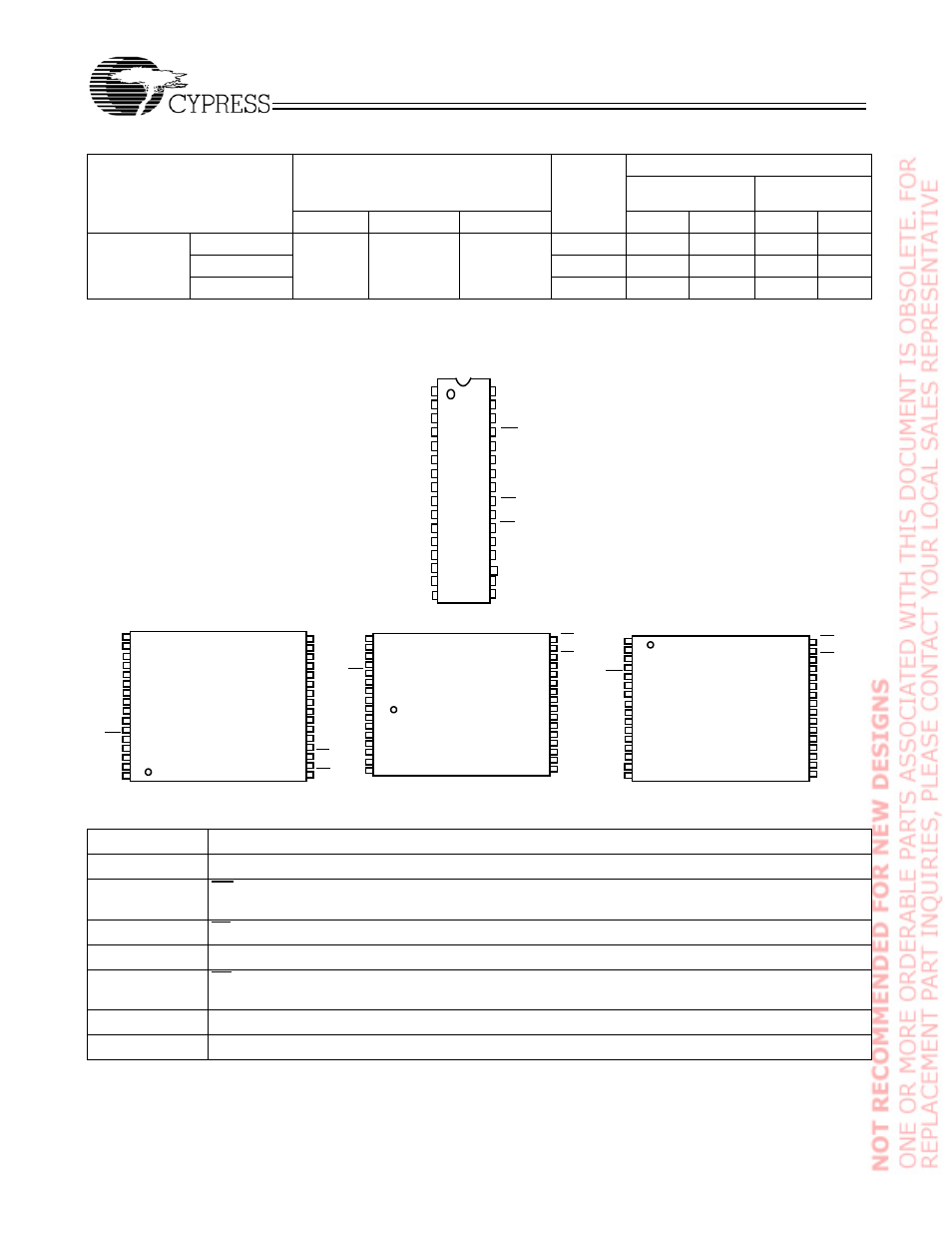

Pin Configurations

Product Portfolio

Product

V

CC

Range (V)

Speed

(ns)

Power Dissipation

Operating, I

CC

(mA)

Standby, I

SB2

(

µA)

Min.

Typ.

[2]

Max.

Typ.

[2]

Max.

Typ.

[2]

Max.

CY62128BLL

Industrial

4.5

5.0

5.5

55

7.5

20

2.5

15

Industrial

70

6

15

2.5

15

Automotive

70

6

25

2.5

25

Pin Definitions

Input

A

0

-A

16

. Address Inputs

Input/Output

I/O

0

-I/O

7

. Data lines. Used as input or output lines depending on operation

Input/Control

WE. Write Enable, Active LOW. When selected LOW, a WRITE is conducted. When selected HIGH, a READ

is conducted.

Input/Control

CE

1

. Chip Enable 1, Active LOW.

Input/Control

CE

2

. Chip Enable 2, Active HIGH.

Input/Control

OE. Output Enable, Active LOW. Controls the direction of the I/O pins. When LOW, the I/O pins behave as

outputs. When deasserted HIGH, I/O pins are three-stated, and act as input data pins

Ground

GND. Ground for the device

Power Supply

V

CC

. Power supply for the device

Note:

2.

Typical values are included for reference only and are not tested or guaranteed. Typical values are an average of the distribution across normal production

variations as measured at V

CC

= 5.0V, T

A

= 25 °C, and t

AA

= 70 ns.

1

2

3

4

5

6

7

8

9

10

11

14

19

20

24

23

22

21

25

28

27

26

Top View

12

13

29

32

31

30

16

15

17

18

A16

A14

A12

A7

A6

A5

A4

A3

WE

V

CC

A15

A13

A8

A9

I/O7

I/O6

I/O5

I/O4

A2

NC

I/O0

I/O1

I/O2

CE1

OE

A10

I/O3

A1

A0

A11

CE2

A

6

A

7

A

16

A

14

A

12

WE

V

CC

A

4

A

13

A

8

A

9

OE

TSOP I

Top View

(not to scale)

1

6

2

3

4

5

7

32

27

31

30

29

28

26

21

25

24

23

22

19

20

I/O

2

I/O

1

GND

I/O

7

I/O

4

I/O

5

I/O

0

CE

1

A

11

A

5

17

18

8

9

10

11

12

13

14

15

16

CE

2

A

15

NC

A

10

I/O

3

A

1

A

0

A

3

A

2

SOIC

A

6

A

7

A

16

A

14

A

12

WE

V

CC

A

4

A

13

A

8

A

9

OE

Reverse TSOP I

1

6

2

3

4

5

7

32

27

31

30

29

28

26

21

25

24

23

22

19

20

I/O

2

I/O

1

GND

I/O

7

I/O

4

I/O

5

I/O

6

I/O

0

CE

1

A

11

A

5

17

18

8

9

10

11

12

13

14

15

16

CE

2

A

15

NC

A

10

I/O

3

A

1

A

0

A

3

A

2

(not to scale)

Top View

A

6

A

7

A

16

A

14

A

12

WE

V

CC

A

4

A

13

A

8

A

9

OE

STSOP

Top View

(not to scale)

25

30

26

27

28

29

31

24

19

23

22

21

20

18

13

17

16

15

14

11

12

I/O

2

I/O

1

GND

I/O

7

I/O

4

I/O

5

I/O

6

I/O

0

CE

1

A

11

A

5

9

10

32

1

2

3

4

5

6

7

8

CE

2

A

15

NC

A

10

I/O

3

A

1

A

0

A

3

A

2

25

GN

gnc

G

g

GND

I/O

6