Digilent 410-134P-KIT User Manual

Page 14

Nexys2 Reference Manual

Digilent

www.digilentinc.com

Copyright Digilent, Inc.

Page 14/17

Doc: 502-134

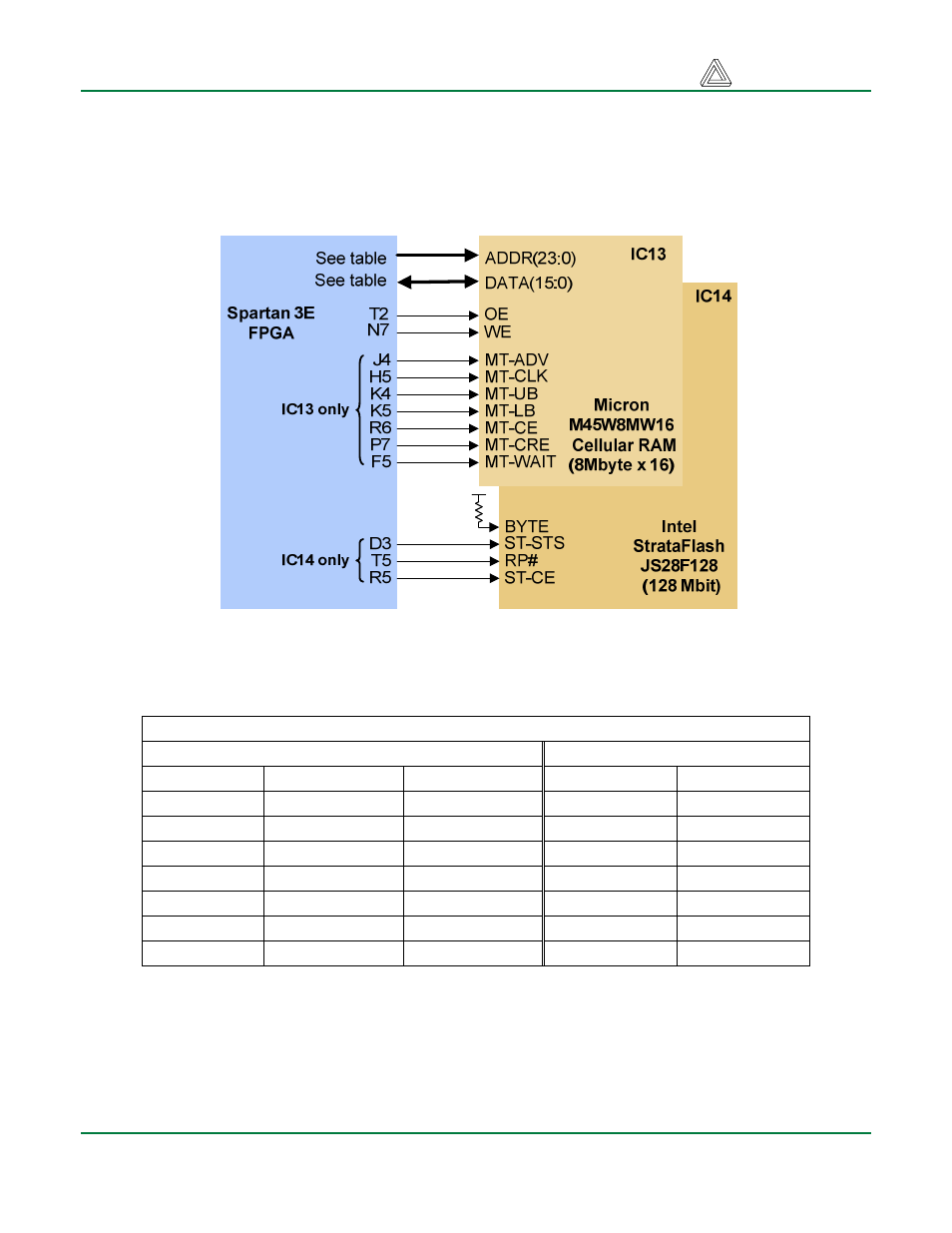

VDHL source code is available in a reference design posted on the Digilent website to illustrate the

use of these devices. A base system builder file is also available for using these devices with Xilinx’s

EDK tool and MicroBlaze processor core, both available from Xilinx. Complete information is available

for both devices from the manufacturer websites.

Table 2: Memory Address and Data Bus Pin Assignments

Address signals

Data signals

ADDR0: NA

ADDR8: H6

ADDR16: M5

DATA0: L1

DATA8: L3

ADDR1: J1

ADDR9: F1

ADDR17: E2

DATA1: L4

DATA9: L5

ADDR2: J2

ADDR10: G3

ADDR18: C2

DATA2: L6

DATA10: M3

ADDR3: H4

ADDR11: G6

ADDR19: C1

DATA3: M4

DATA11: M6

ADDR4: H1

ADDR12: G5

ADDR20: D2

DATA4: N5

DATA12: L2

ADDR5: H2

ADDR13: G4

ADDR21: K3

DATA5: P1

DATA13: N4

ADDR6: J5

ADDR14: F2

ADDR22: D1

DATA6: P2

DATA14: R3

ADDR7: H3

ADDR15: E1

ADDR23: K6

DATA7: R2

DATA15: T1

Figure 22: Nexys2 memory circuits