Pin definitions – Cypress CY7C1446AV33 User Manual

Page 6

CY7C1440AV33

CY7C1442AV33

CY7C1446AV33

Document #: 38-05383 Rev. *E

Page 6 of 31

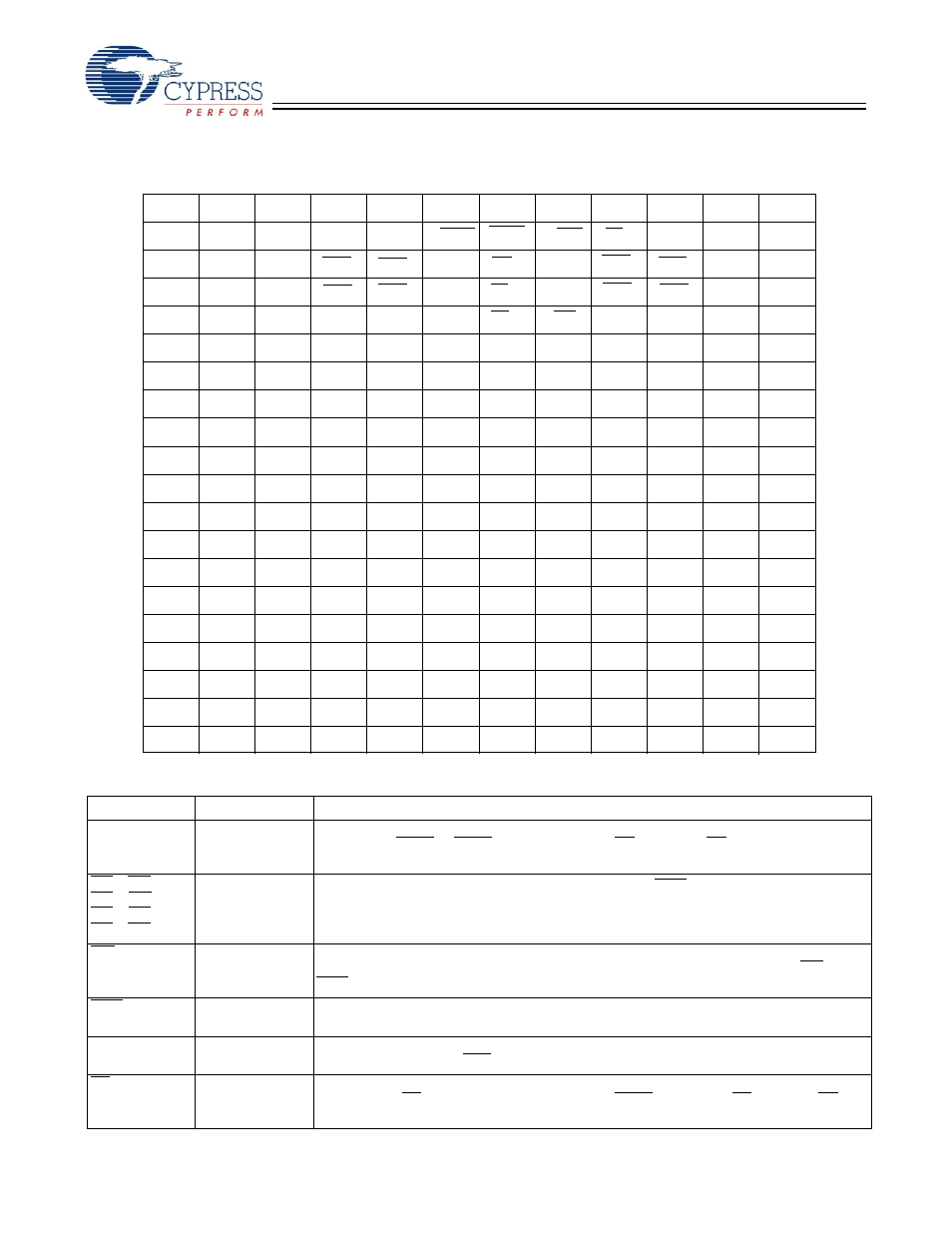

209-ball FBGA (14 x 22 x 1.76 mm) Pinout

CY7C1446AV33 (512K × 72)

Pin Configurations

(continued)

A

B

C

D

E

F

G

H

J

K

L

M

N

P

R

T

U

V

W

1

2

3

4

5

6

7

8

9

11

10

DQ

G

DQ

G

DQ

G

DQ

G

DQ

G

DQ

G

DQ

G

DQ

G

DQ

C

DQ

C

DQ

C

DQ

C

NC

DQP

G

DQ

H

DQ

H

DQ

H

DQ

H

DQ

D

DQ

D

DQ

D

DQ

D

DQP

D

DQP

C

DQ

C

DQ

C

DQ

C

DQ

C

NC

DQ

H

DQ

H

DQ

H

DQ

H

DQP

H

DQ

D

DQ

D

DQ

D

DQ

D

DQ

B

DQ

B

DQ

B

DQ

B

DQ

B

DQ

B

DQ

B

DQ

B

DQ

F

DQ

F

DQ

F

DQ

F

NC

DQP

F

DQ

A

DQ

A

DQ

A

DQ

A

DQ

E

DQ

E

DQ

E

DQ

E

DQP

A

DQP

B

DQ

F

DQ

F

DQ

F

DQ

F

NC

DQ

A

DQ

A

DQ

A

DQ

A

DQP

E

DQ

E

DQ

E

DQ

E

DQ

E

A

ADSP

ADV

A

NC

NC

NC/72M

A

A

A

A

A

A

A

A

A

A1

A0

A

A

A

A

A

A

NC/144M

NC/288M

NC/576M

GW

NC

NC

BWS

B

BWS

F

BWS

E

BWS

A

BWS

C

BWS

G

BWS

D

BWS

H

TMS

TDI

TDO

TCK

NC

NC

MODE

NC

V

SS

V

SS

NC

CLK

NC

V

SS

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

DD

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

NC/1G

V

DD

NC

OE

CE

3

CE

1

CE

2

ADSC

BW

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

ZZ

V

SS

V

SS

V

SS

V

SS

NC

V

DDQ

V

SS

V

SS

NC

V

SS

V

SS

V

SS

V

SS

V

SS

V

SS

NC

V

SS

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

NC

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

V

DDQ

Pin Definitions

Name

I/O

Description

A

0

, A

1

, A

Input-

Synchronous

Address Inputs used to select one of the address locations. Sampled at the rising edge

of the CLK if ADSP or ADSC is active LOW, and CE

1

,

CE

2

, and

CE

3

[2]

are sampled active.

A1: A0 are fed to the two-bit counter.

BW

A

, BW

B

,

BW

C

, BW

D

,

BW

E

, BW

F

,

BW

G

, BW

H

Input-

Synchronous

Byte Write Select Inputs, active LOW. Qualified with BWE to conduct byte writes to the

SRAM. Sampled on the rising edge of CLK.

GW

Input-

Synchronous

Global Write Enable Input, active LOW. When asserted LOW on the rising edge of CLK,

a global write is conducted (ALL bytes are written, regardless of the values on BW

X

and

BWE).

BWE

Input-

Synchronous

Byte Write Enable Input, active LOW. Sampled on the rising edge of CLK. This signal

must be asserted LOW to conduct a byte write.

CLK

Input-

Clock

Clock Input. Used to capture all synchronous inputs to the device. Also used to increment

the burst counter when ADV is asserted LOW, during a burst operation.

CE

1

Input-

Synchronous

Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction

with CE

2

and CE

3

to select/deselect the device. ADSP is ignored if CE

1

is HIGH. CE

1

is

sampled only when a new external address is loaded.