Cypress CY7C145 User Manual

8k x 8/9 dual-port static ram with sem, int, busy, Features, Functional description

CY7C145, CY7C144

8K x 8/9 Dual-Port Static RAM

with SEM, INT, BUSY

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document #: 38-06034 Rev. *D

Revised December 10, 2008

Features

■

True Dual-Ported memory cells that enable simultaneous

reads of the same memory location

■

8K x 8 organization (CY7C144)

■

8K x 9 organization (CY7C145)

■

0.65-micron CMOS for optimum speed and power

■

High speed access: 15 ns

■

Low operating power: I

CC

= 160 mA (max.)

■

Fully asynchronous operation

■

Automatic power down

■

TTL compatible

■

Master/Slave select pin enables bus width expansion to

16/18 bits or more

■

Busy arbitration scheme provided

■

Semaphores included to permit software handshaking

between ports

■

INT flag for port-to-port communication

■

Available in 68-pin PLCC, 64-pin and 80-pin TQFP

■

Pb-free packages available

Functional Description

The CY7C144 and CY7C145 are high speed CMOS 8K x 8

and 8K x 9 dual-port static RAMs. Various arbitration schemes

are included on the CY7C144/5 to handle situations when

multiple processors access the same piece of data. Two ports

are provided permitting independent, asynchronous access

for reads and writes to any location in memory. The

CY7C144/5 can be used as a standalone 64/72-Kbit dual-port

static RAM or multiple devices can be combined in order to

function as a 16/18-bit or wider master/slave dual-port static

RAM. An M/S pin is provided for implementing 16/18-bit or

wider memory applications without the need for separate

master and slave devices or additional discrete logic. Appli-

cation areas include interprocessor/multiprocessor designs,

communications status buffering, and dual-port

video/graphics memory.

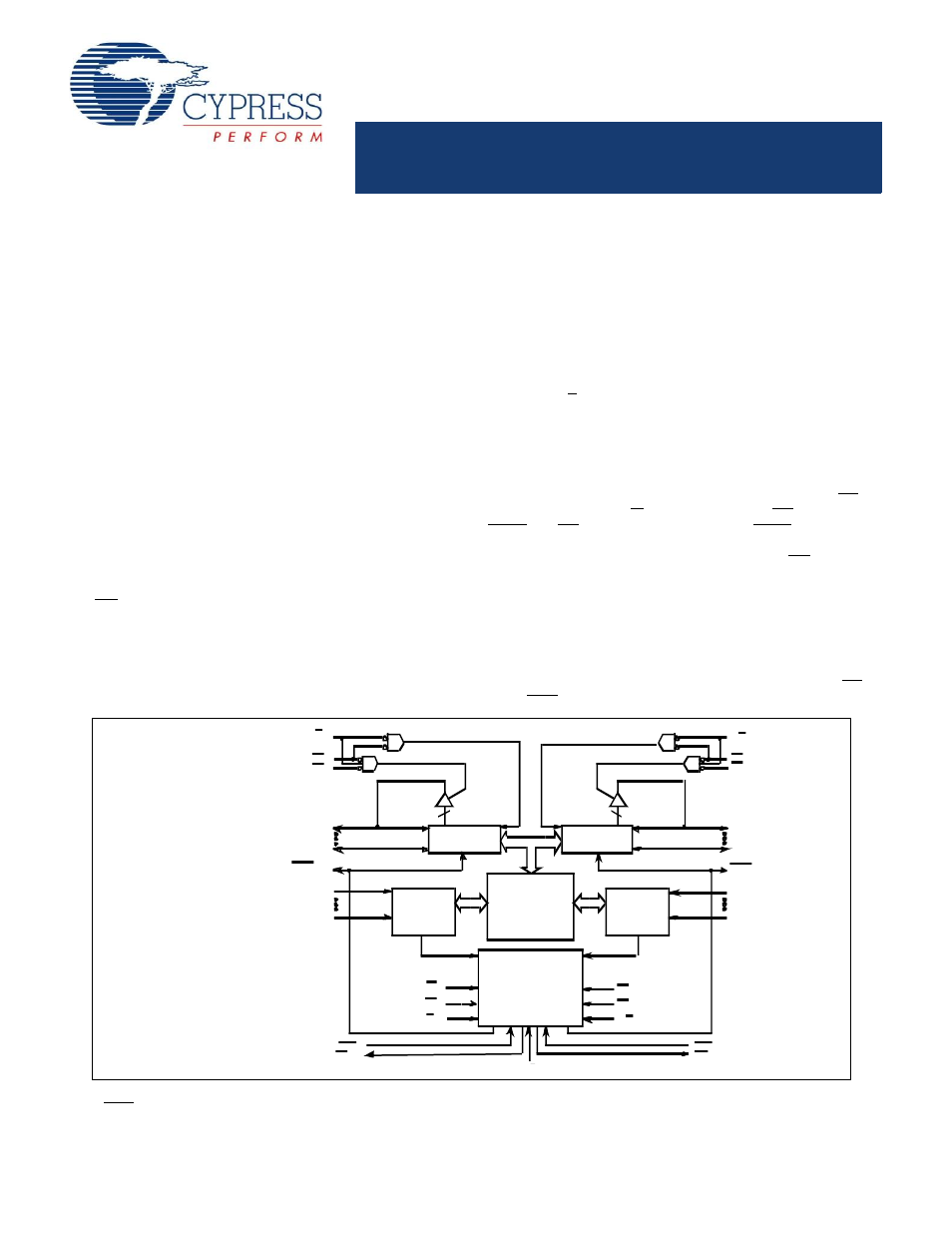

Each port has independent control pins: chip enable (CE),

read or write enable (R/W), and output enable (OE). Two flags,

BUSY and INT, are provided on each port. BUSY signals that

the port is trying to access the same location currently being

accessed by the other port. The interrupt flag (INT) permits

communication between ports or systems by means of a mail

box. The semaphores are used to pass a flag, or token, from

one port to the other to indicate that a shared resource is in

use. The semaphore logic is comprised of eight shared

latches. Only one side can control the latch (semaphore) at

any time. Control of a semaphore indicates that a shared

resource is in use. An automatic power down feature is

controlled independently on each port by a chip enable (CE)

pin or SEM pin.

Notes

1. BUSY is an output in master mode and an input in slave mode.

2. Interrupt: push-pull output and requires no pull-up resistor.

R/ W L

CE L

OE L

A 12L

A 0L

A 0R

A 12R

R/ W R

CE R

OE R

CE R

OE R

CEL

OE L

R/ W L

R/W R

I /O7L

I /O0L

I/O 7R

I/O 0R

INT ERRUP T

SE MA P HORE

ARB I TRAT IO N

CONT ROL

I/ O

CONT ROL

I /O

M EM ORY

A RRA Y

A DDRES S

DECODE R

ADDRE SS

DE CODE R

SE M L

SE MR

B US YL

BUS Y R

I NTL

INTR

M /S

(7C145) I /O8L

I/O 8R(7C14 5)

[1, 2]

[ 2]

[1, 2]

[ 2]

Logic Block Diagram

CY7C144 CY7C1458K x 8/9 Dual-Port Static RAM

with SEM, INT, BUSY

Document Outline

- Features

- Functional Description

- Logic Block Diagram

- Pin Configurations

- Maximum Ratings

- Operating Range

- Electrical Characteristics Over the Operating Range

- Capacitance

- Switching Characteristics Over the Operating Range[9]

- Switching Waveforms

- Architecture

- Functional Description

- Ordering Information

- Package Diagrams

- Document History Page

- Sales, Solutions and Legal Information