Kontron VM62 User Manual

Page 30

VM62(A) / VM42(A) User’s Manual

Chapter 2 Functional Description

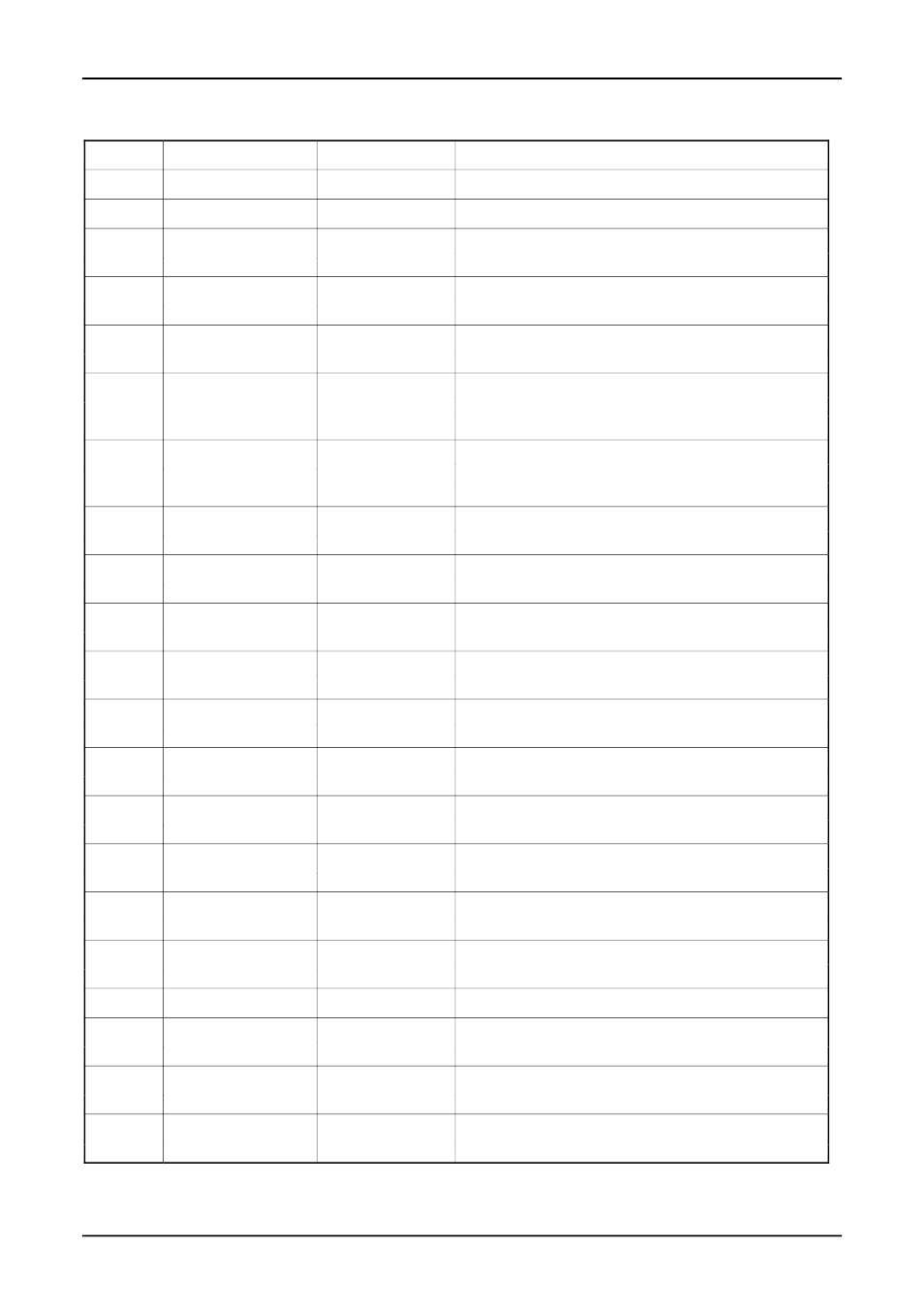

Table 2.5.3.2: Further Explanation of 68(EN)360 Mnemonics

Group

Signal Name

Mneumonic

Function

SCC

Receive Data

RXD4-RXD1

Serial receive data input to the SCCs (I)

Transmit Data

TXD4-TXD1

Serial transmit data output from the SCCs (O)

Request to Send

_RTS4-_RTS1

Request to send outputs indicate that the SCC is ready

to transmit data (O)

Clear to Send

_CTS4-_CTS1

Clear to send inputs indicate to the SCC that data

transmission may begin (I)

Carrier Detect

_CD4-_CD1

Carrier detect inputs indicate that the SCC should begin

reception of data (I)

Receive Start

_RSTRT1

This output from SCC1 identifies the start of a receive

frame. Can be used by an Ethernet CAM to perform

address matching (O)

Receive Reject

RRJCT1

This input to SCC1 allows a CAM to reject the current

Ethernet frame after it determines the frame address did

not match (I)

Clocks

CLK8-CLK1

Input clocks to the SCCs, SMCs, SI, and the baud rate

generators (I)

IDMA

DMA Request

_DREQ2-

_DREQ1

A request (input) to an IDMA channel to start an

IDMA transfer (I)

DMA Acknowledge

_DACK2-

_DACK1

An acknowledgement (output) by the IDMA that an

IDMA transfer is in progress (O)

DMA Done

_DONE2-

_DONE1

A bidirectional signal that indicates the last IDMA

transfer in a block of data (I/O)

TIMER

Timer Gate

_TGATE2-

_TGATE1

An input to a timer that enables/disables the counting

function (I)

Timer Input

TIN4-TIN1

Time reference input to the timer that allows it to

function as a counter (I)

Timer Output

_TOUT4-

_TOUT1

Output waveform (pulse or toggle) from the timer as a

result of a reference value being reached (O)

SPI

SPI Master-In

Slave-Out

SPIMISO

Serial data input to the SPI master (I); serial data

output from an SPI slave (O)

SPI Master-Out

Slave-In

SPIMOSI

Serial data output from the SPI master (O); serial data

input to an SPI slave (I)

SPI Clock

SPICLK

Output clock from the SPI master (O); input clock to

the SPI slave (I)

SPI Select

_SPISEL

SPI slave select input (I)

SMC

SMC Receive Data

SMRXD2-

SMRXD1

Serial data input to the SMCs (I)

SMC Transmit Data

SMTXD2-

SMTXD1

Serial data output from the SMCs (O)

SMC Sync

_SMSYN2-

_SMSYN1

SMC syncronization signal (I)

May 17, 1996

© 1995 PEP Modular Computers

Page 2-15