3 primary address decoder, 4 secondary address decoder – Kontron VM62 User Manual

Page 18

VM62(A) / VM42(A) User’s Manual

Chapter 2 Functional Description

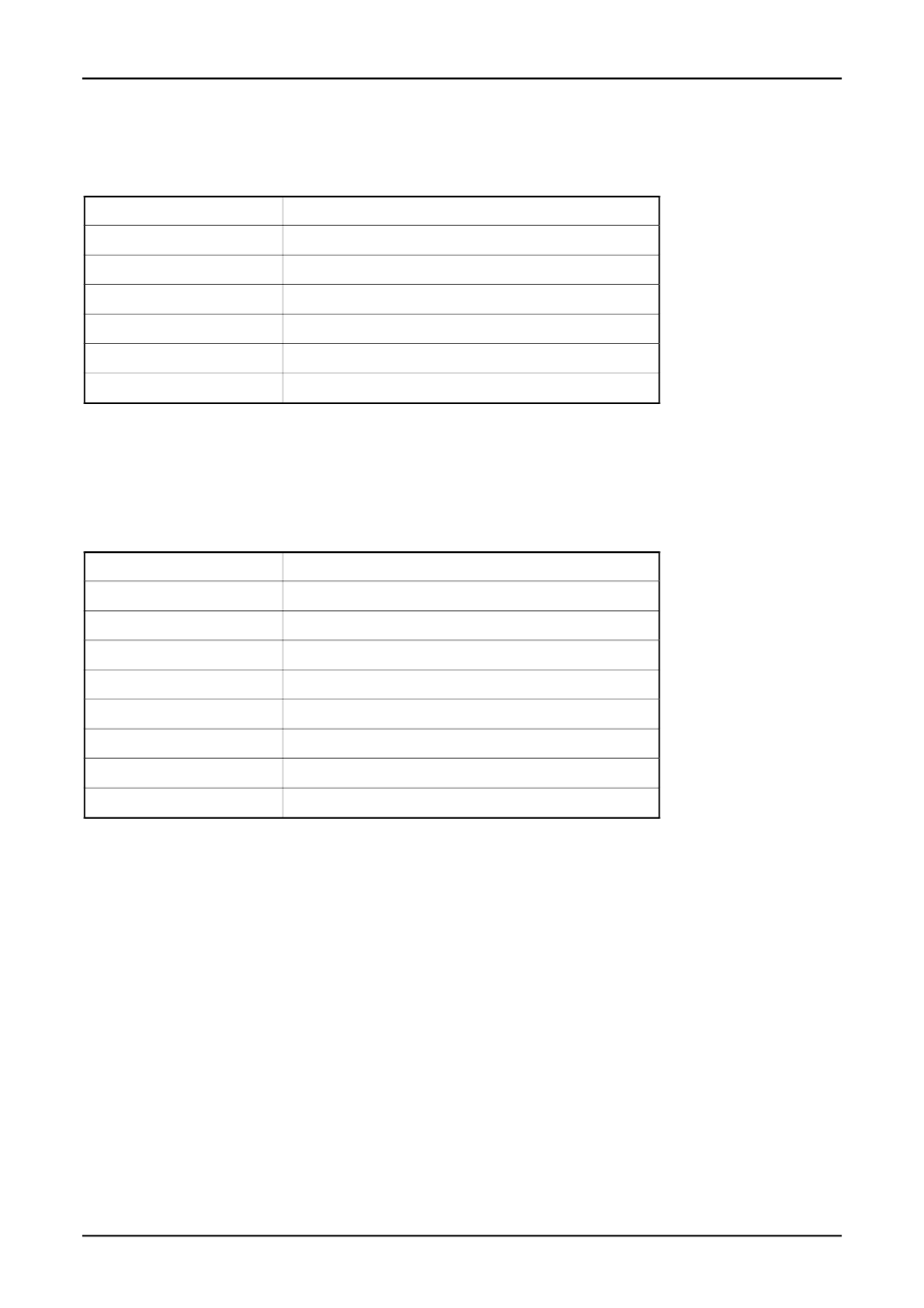

2.2.3 Primary Address Decoder

The primary address decoder generates the following select signals.

CS_360

Secondary address decoder (68EN360, DRAM, FLASH)

CS_VME

VMEbus address range

CS_AUT

AutoBahn Interface address range

CS_BSS

Bussizer address range (VME, SRAM, AutoBahn, I/O)

BERR_0

Reserved address range (Bus Error)

EN_BSS

68EN360 DMA address range

IACK

Interrupt Acknowledge Cycle

2.2.4 Secondary Address Decoder

The secondary address decoder is built by the 68EN360 chip select logic and is therefore programmable. The outputs are

used as base address selects, as shown below.

68EN360 Chip Select

Connected to

CS0

FLASH

CS1

DRAM

CS2

VME via 68EN360 DMA

CS3

AutoBahn Interface

CS4

SRAM

CS5

CXC

CS6

RTC

CS7

Control / Status Registers

May 17, 1996

© 1995 PEP Modular Computers

Page 2-3