4 programming interface, 1 access control logic (address decoder), 4 programming interface - 8 – Kontron CP384 User Manual

Page 54: Access control logic (address decoder) - 8, Configuration cp384

Kontron Modular Computers GmbH

ID 31440, Rev. 01

P R E L I M I N A R Y

Re

vNr. = CP384

-

31440

_01 -

06

0503

/14

4230

Page 4 - 8

Configuration

CP384

4.4

Programming Interface

4.4.1

Access Control Logic (Address Decoder)

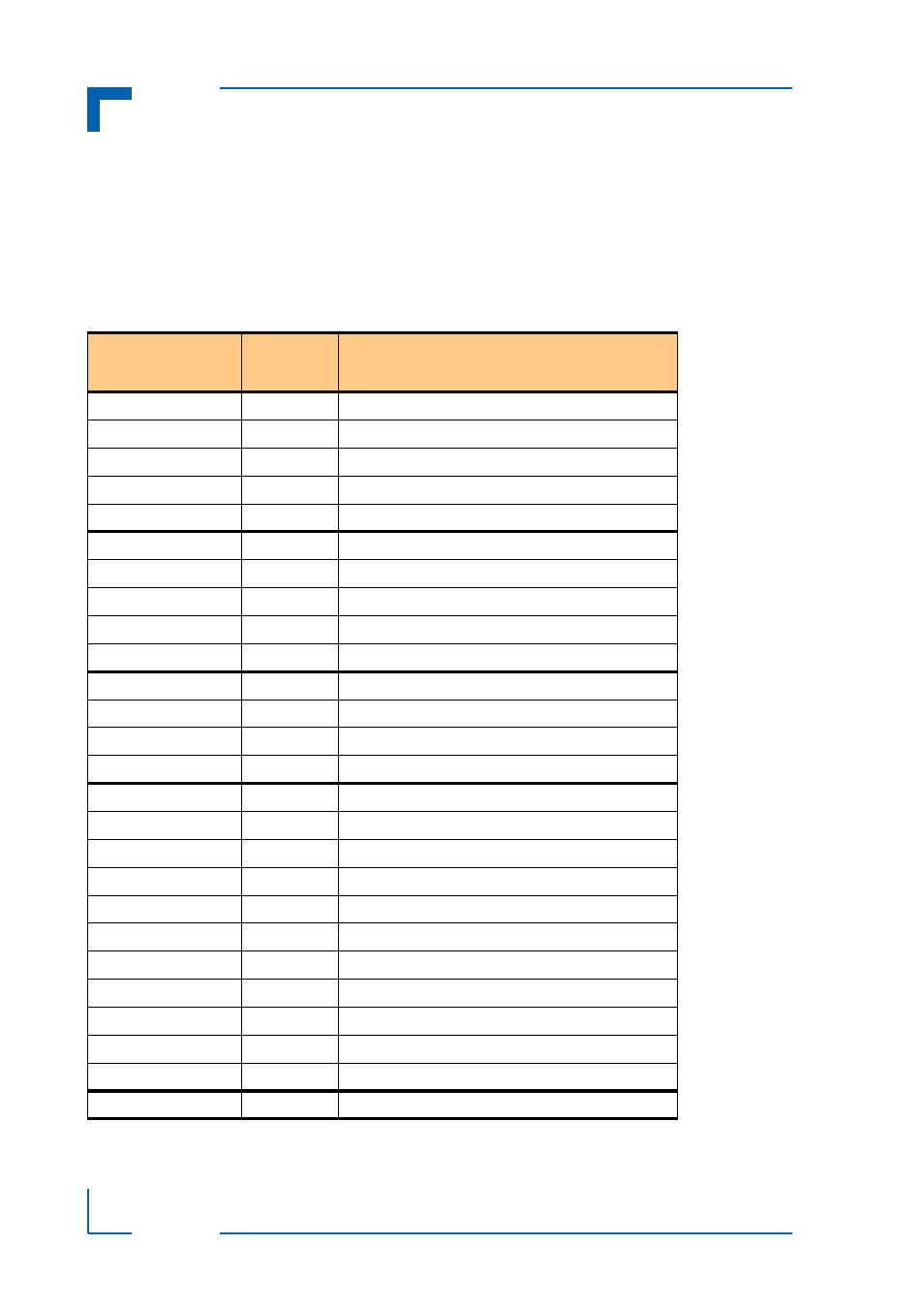

All the resources of the CP384 are mapped within the 64 kB PCI memory address space which

itself is set in the PCI configuration register BAR0. The port size of all local or backend registers

is 32-bit by default. The address map of the registers is as follows.

Table 4-1: Backend Register Address Map

BASE ADDRESS

(BAR0)

SIZE

FUNCTION

+ 0x0000

4 kB

COMMON BOARD REGISTER

0x0400

32 bit

g_irq

General Interrupt Enable Register

0x0800

32 bit

hsr

Hardware Status Register

0x0804

32 bit

i_pen

General Interrupt Pending Register

0x0C00

32 bit

hdr

Hardware Debug Register

+ 0x1000

4 kB

CAPABILITY ROM, SERIAL EEPROM

0x1000

32 bit

r_cmd

Command Register

0x1400

32 bit

r_ctl

Control Register

0x1800

32 bit

r_sta

Status Regsiter

0x1C00

32 bit

r_dat

Data Register

+ 0x2000

4 kB

DIGOUT CLUSTER

0x2400

32 bit

o_ctl_a Output Control Register

0x2800

32 bit

o_sta_a Output Status Register

0x2C00

32 bit

o_dat_a Output Data Register

+ 0x4000

4 kB

DIGIN CLUSTER

0x4400

32 bit

i_ctl

Input Control Register

0x4408

32 bit

i_irquen Input Irq Enable Register

0x440C

32 bit

e_pol

Input Event Polarity Register

0x4410

32 bit

e_msk Input Event Mask Register

0x4414

32 bit

e_len

Input Latch-on Event Register

0x4418

32 bit

c_cmp

Input Pattern Compare Register

0x441C

32 bit

c_msk

Input Pattern Mask Register

0x4800

32 bit

i_event Input Status Register

0x4C00

32 bit

d_in

Input Data Register

0x4C04

32 bit

input

Transparent Input Data

+ 0x5000

44 kB

Reserved