Achronix Speedster22i Pin Connections and Power Sequencing User Manual

Page 9

UG042, August 19, 2014

9

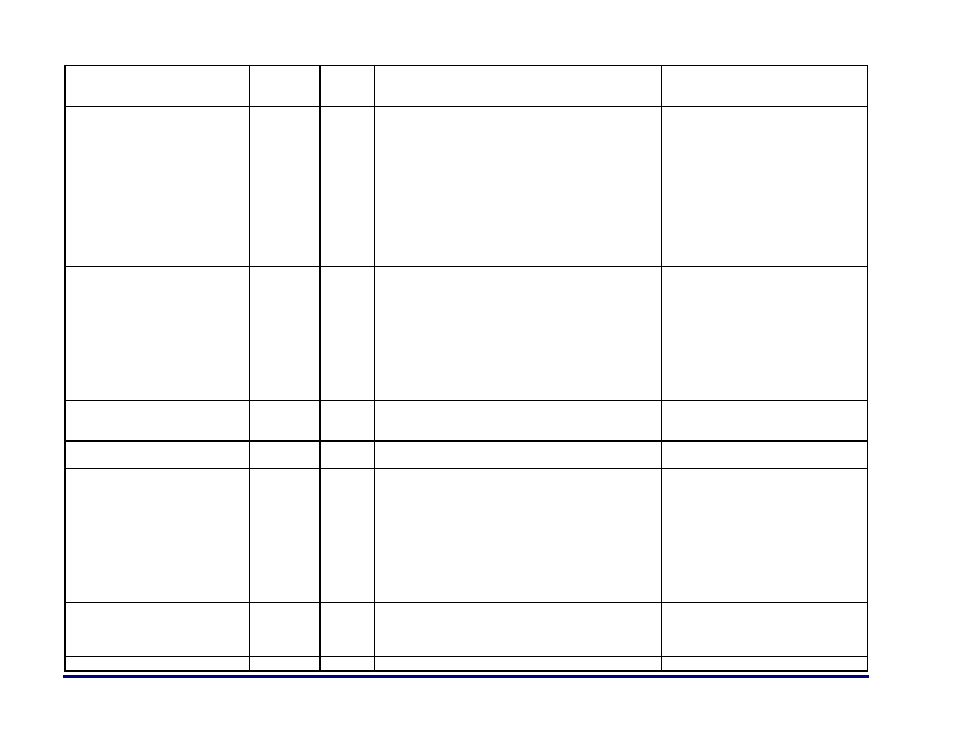

AVDD_PLL_[SE, SW, NE, NW][3:0]

PLL

Power

Analog power supply for the PLLs feeding the FPGA core

fabric.

Connect all 1.7V AVDD_PLL pins to a linear

or low noise switching power supply. This is

a highly sensitive PLL analog power supply.

VDDO_JCFG

CFG

Power

Supply voltage powering the I/O buffers for the IEEE 1149.1

JTAG interface. The value selected determine the output VOH

level on TDO and set the input threshold VIL and VIH values

appropriately. (TAP) controller state machine transitions. This

input is captured on the rising edge of the test logic clock

(TCK). This dedicated pin is equipped with a pull-up resistor to

place the test logic in the Test-Logic-Reset state

Connect these pins to a 1.8V power supply.

This supply can be shared with the 1.8V

analog SerDes power supply (PA_VDD2).

Noise should not be a concern, since the

JTAG I/O buffers and SerDes will generally

not operate the same time. The one

exception is during in-system debug with

Snapshot, which should still be fine.

However, it would be preferable to have

this power supply be shared with a 1.8V

VDDO_B[xx] I/O power supply if 1.8V I/Os

are used in the design.

VDDL

CVDD

Power

Power Supply for FPGA fabric core logic

VDDL is the 1.0V core supply. Connect all

VDDL pins to a low noise switching

regulator. While VDDL is one of many 1.0V

supplies, it is recommended that a separate

regulator be used to ensure noise isolation

and for prevention of current spikes prior

to clearing of the configuration memory.

Refer to the supply power up/down

requirements below for further

information.

VCC

SVDD

Power

Digital Power Supply for FPGA circuitry in the I/O ring,

including the Hard IP.

Connect VCC to a 1.0V linear regulator. This

supply can be shared with VDD_CFG and

VDD_BRAM.

VCCRAM_EFUSE[3:1]

EFUSE

Power

Efuse Power Supply normal / read operations

Tie this to the 1.0V supply powering

VDDA_NOM_E/W

VCCFHV_EFUSE[3:1]

FFUSE

Power

Efuse Power Supply for Fuse Program / Erase operations

If the application requires fuse blowing (eg.

programming encryption fuses for design

security), this supply needs to be tied to a

regulator capable of providing output

voltages in the 1.0V – 2.2V range. For these

cases, this supply cannot be shared with

any other supply. If fuse blowing is not

needed, this supply can be tied to the 1.0V

regulator powering VDDA_NOM_E/W and

VCCRAM_EFUSE[3:1].

VDDA_NOM_E

EVDDA

Power

Analog Power Supply for FPGA circuitry in the I/O ring.

Connect VDDA_NOM_E to a 1.0V linear

regulator. The only 1.0V supplies that can

be shared with this supply are the eFuse

power supplies.

VDD_CFG

CFG

Power

Supply voltage for the configuration memory SRAM cells in

Connect VDD_CFG to a 1.0V linear