Sl811hs – Cypress SL811HS User Manual

Page 6

SL811HS

Document 38-08008 Rev. *D

Page 6 of 32

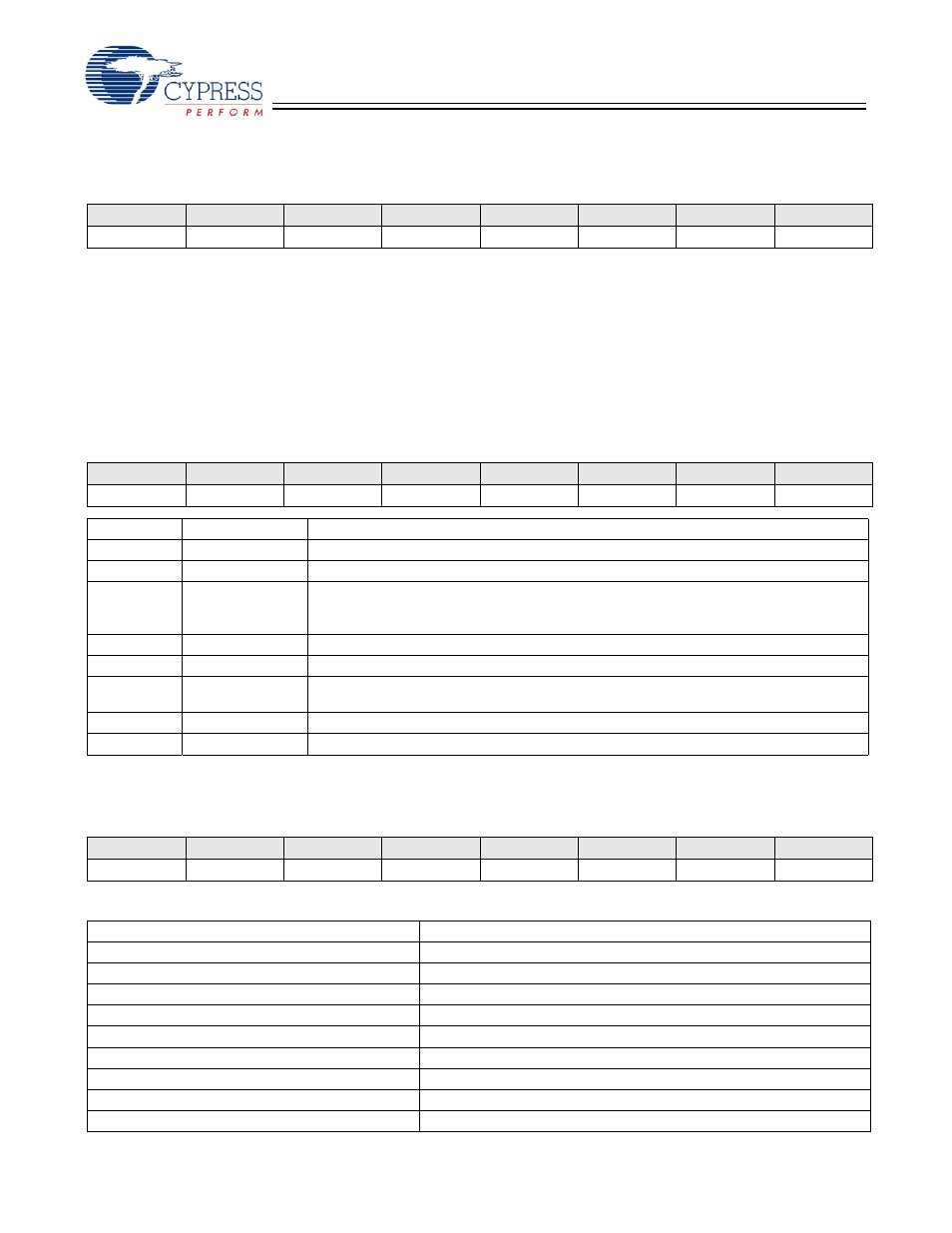

USB-A/USB-B Host Base Length [Address = 02h, 0Ah].

The USB A/B Host Base Length register contains the maximum packet size transferred between the SL811HS and a slave USB

peripheral. Essentially, this designates the largest packet size that is transferred by the SL811HS. Base Length designates the

size of data packet sent or received. For example, in full speed BULK mode, the maximum packet length is 64 bytes. In ISO

mode, the maximum packet length is 1023 bytes since the SL811HS only has an 8-bit length; the maximum packet size for the

ISO mode using the SL811HS is 255 – 16 bytes (register space). When the Host Base length register is set to zero, a Zero-Length

packet is transmitted.

USB-A/USB-B USB Packet Status (Read) and Host PID, Device Endpoint (Write) [Address = 03h, 0Bh]. This register has

two modes dependent on whether it is read or written. When read, this register provides packet status and contains information

relative to the last packet that has been received or transmitted. This register is not valid for reading until after the Done interrupt

occurs, which causes the register to update.

When written, this register provides the PID and Endpoint information to the USB SIE engine used in the next transaction. All 16

Endpoints can be addressed by the SL811HS.

PID[3:0]: 4-bit PID Field (See Table Below), EP[3:0]: 4-bit Endpoint Value in Binary.

Table 5.

USB-A / USB-B Host Base Length Definition [Address 02h, 0Ah]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

HBL7

HBL6

HBL5

HBL4

HBL3

HBL2

HBL1

HBL0

Table 6.

USB-A/USB-B USB Packet Status Register Definition when READ [Address 03h, 0Bh]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

STALL

NAK

Overflow

Setup

Sequence

Time-out

Error

ACK

Bit Position

Bit Name

Function

7

STALL

Slave device returned a STALL.

6

NAK

Slave device returned a NAK.

5

Overflow

Overflow condition - maximum length exceeded during receives. For underflow, see

USB-A/USB-B Host Transfer Count Register (Read), USB Address (Write) [Address = 04h,

0Ch] on page 7

.

4

Setup

This bit is not applicable for Host operation since a SETUP packet is generated by the host.

3

Sequence

Sequence bit. ’0’ if DATA0, ’1’ if DATA1.

2

Time-out

Timeout occurred. A timeout is defined as 18-bit times without a device response (in full

speed).

1

Error

Error detected in transmission. This includes CRC5, CRC16, and PID errors.

0

ACK

Transmission Acknowledge.

Table 7.

USB-A / USB-B Host PID and Device Endpoint Register when WRITTEN [Address 03h, 0Bh]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

PID3

PID2

PID1

PID0

EP3

EP2

EP1

EP0

PID TYPE

D7-D4

SETUP

1101 (D Hex)

IN

1001 (9 Hex)

OUT

0001 (1 Hex)

SOF

0101 (5 Hex)

PREAMBLE

1100 (C Hex)

NAK

1010 (A Hex)

STALL

1110 (E Hex)

DATA0

0011 (3 Hex)

DATA1

1011 (B Hex)