Sl811hs – Cypress SL811HS User Manual

Page 16

SL811HS

Document 38-08008 Rev. *D

Page 16 of 32

Interrupt Enable Register, Address [06h] . The SL811HS

provides an Interrupt Request Output that is activated

resulting from a number of conditions. The Interrupt Enable

register allows the user to select events that generate the

Interrupt Request Output assertion. A separate Interrupt

Status register is read in order to determine the condition that

initiated the interrupt (see the description in section

Status Register, Address [0Dh]

). When a bit is set to ‘1’, the

corresponding interrupt is enabled. Setting a bit in the Interrupt

Enable register does not effect the Interrupt Status register’s

value; it just determines which interrupts are output on INTRQ.

USB Address Register, Address [07h]. This register

contains the USB Device Address after assignment by USB

host during configuration. On power up or reset, USB Address

register is set to Address 00h. After USB configuration and

address assignment, the device recognizes only USB transac-

tions directed to the address contained in the USB Address

register.

Interrupt Status Register, Address [0Dh]. This read/write

register serves as an Interrupt Status register when it is read,

and an Interrupt Clear register when it is written. To clear an

interrupt, write the register with the appropriate bit set to ‘1’.

Writing a ‘0’ has no effect on the status.

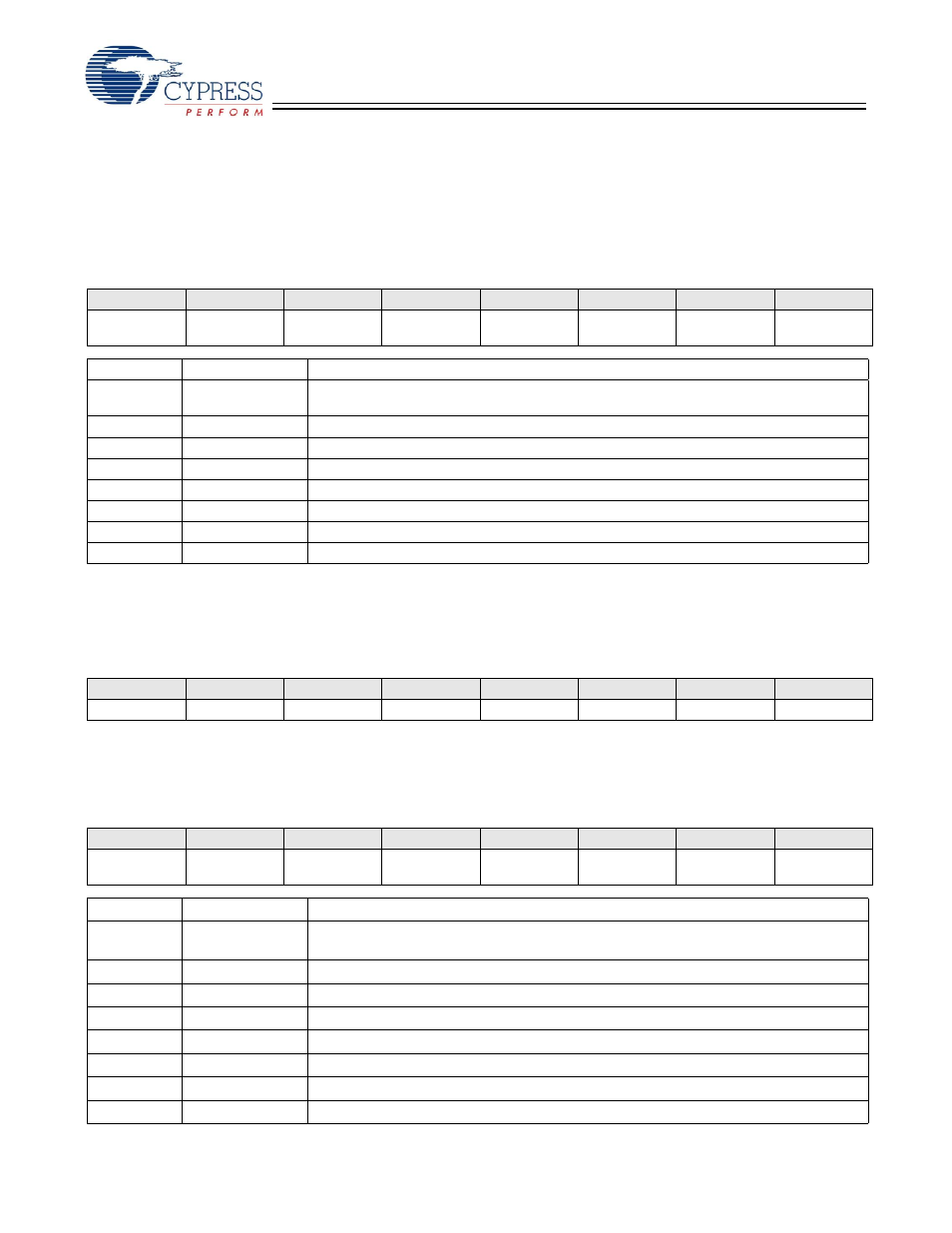

Table 30. Interrupt Enable Register [Address: 06h]

7

6

5

4

3

2

1

0

DMA Status

USB Reset

SOF Received

DMA Done

Endpoint 3

Done

Endpoint 2

Done

Endpoint 1

Done

Endpoint 0

Done

Bit Position

Bit Name

Function

7

DMA Status

When equal to ‘1’, indicates DMA transfer is in progress. When equal to ‘0’, indicates DMA

transfer is complete.

6

USB Reset

Enable USB Reset received interrupt when = ‘1’.

5

SOF Received

Enable SOF Received Interrupt when = ‘1’.

4

DMA Done

Enable DMA done Interrupt when = ‘1’.

3

Endpoint 3 Done

Enable Endpoint 3 done Interrupt when = ‘1’.

2

Endpoint 2 Done

Enable Endpoint 2 done Interrupt when = ‘1’.

1

Endpoint 1 Done

Enable Endpoint 1 done Interrupt when = ‘1’.

0

Endpoint 0 Done

Enable Endpoint 0 done Interrupt when = ‘1’.

Table 31. USB Address Register [Address 07h]

7

6

5

4

3

2

1

0

USBADD7

USBADD6

USBADD5

USBADD4

USBADD3

USBADD2

USBADD1

USBADD0

Table 32. Interrupt Status Register [Address 0Dh]

7

6

5

4

3

2

1

0

DMA Status

USB Reset

SOF Received

DMA Done

Endpoint 3

Done

Endpoint 2

Done

Endpoint 1

Done

Endpoint 0

Done

Bit Position

Bit Name

Function

7

DMA Status

When equal to ‘1’, indicates DMA transfer is in progress. When equal to 0, indicates DMA

transfer is complete. An interrupt is not generated when DMA is complete.

6

USB Reset

USB Reset Received Interrupt.

5

SOF Received

SOF Received Interrupt.

4

DMA Done

DMA Done Interrupt.

3

Endpoint 3 Done

Endpoint 3 Done Interrupt.

2

Endpoint 2 Done

Endpoint 2 Done Interrupt.

1

Endpoint 1 Done

Endpoint 1 Done Interrupt.

0

Endpoint 0 Done

Endpoint 0 Done Interrupt.