Bus interface timing requirements, I/o write cycle, Sl811hs – Cypress SL811HS User Manual

Page 26

SL811HS

Document 38-08008 Rev. *D

Page 26 of 32

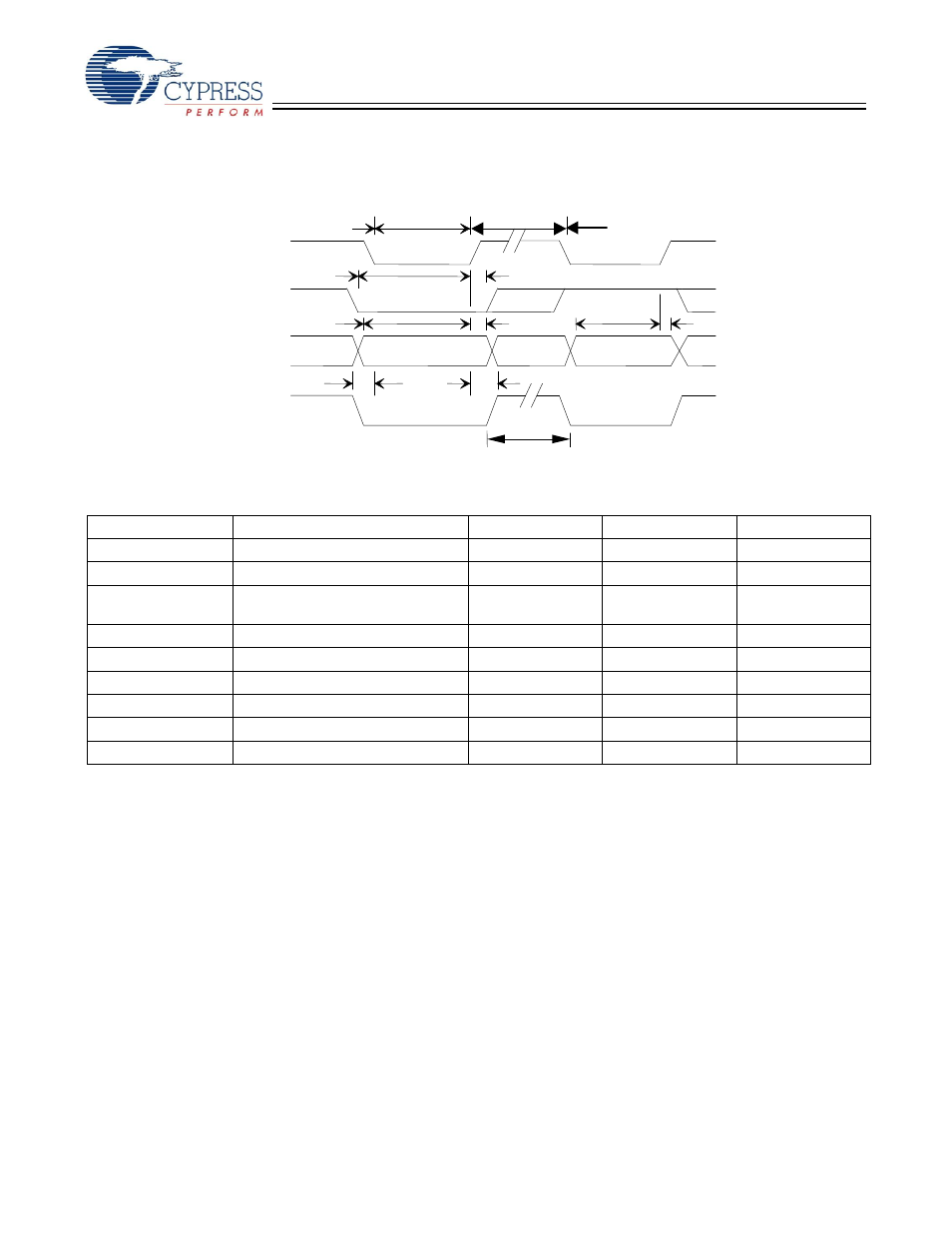

Bus Interface Timing Requirements

I/O Write Cycle

Note nCS an be held LOW for multiple Write cycles provided nWR is cycled. Write Cycle Time for Auto Inc Mode Writes is 170

ns minimum.

nWR

A0

D0-D7

DATA

twr

twahld

twdhld

twasu

twdsu

twdsu

twdhld

I/O Write Cycle to Register or Memory Buffer

Register or Memory

Address

nCS

twcsu

twshld

Tcscs See Note.

twrhigh

Parameter

Description

Min.

Typ.

Max.

t

WR

Write pulse width

85 ns

t

WCSU

Chip select set-up to nWR LOW

0 ns

t

WSHLD

Chip select hold time

After nWR HIGH

0 ns

t

WASU

A0 address set-up time

85 ns

t

WAHLD

A0 address hold time

10 ns

t

WDSU

Data to Write HIGH set-up time

85 ns

t

WDHLD

Data hold time after Write HIGH

5 ns

t

CSCS

nCS inactive to nCS* asserted

85 ns

t

WRHIGH

NWR HIGH

85 ns

See also other documents in the category Cypress Hardware:

- CY7C1410AV18 (29 pages)

- CY7C1411JV18 (28 pages)

- CY7C1383FV25 (28 pages)

- CY14B256L (18 pages)

- CY7C1307BV25 (21 pages)

- CY7C1041DV33 (13 pages)

- CY62167EV18 (13 pages)

- Perform CY7C1565V18 (28 pages)

- STK11C68-5 (15 pages)

- 7C185-20 (11 pages)

- CY7C1168V18 (27 pages)

- CY7C1318CV18-250BZC (26 pages)

- CY7C1364C (18 pages)

- Perform CY7C1382D (34 pages)

- CY7C106D (11 pages)

- CY14E102N (21 pages)

- CY7C1418AV18 (31 pages)

- enCoRe CY7C638xx (83 pages)

- CY7C1018DV33 (9 pages)

- CY7C1292DV18 (23 pages)

- CY7C130 (19 pages)

- CY7C1424BV18 (30 pages)

- CY62157EV18 (12 pages)

- CY7C1392BV18 (31 pages)

- CY7C1302DV25 (18 pages)

- Perform CY7C1511KV18 (31 pages)

- West Bridge Astoria AN46860 (4 pages)

- CY7C1386FV25 (30 pages)

- CY7C1163V18 (29 pages)

- CY7C1266V18 (27 pages)

- CY7C1334H (13 pages)

- CY7C1018CV33 (7 pages)

- CY62136VN (12 pages)

- AN20639 (3 pages)

- CY7C1338G (17 pages)

- CY7C1462AV33 (27 pages)

- CY7C1145V18 (28 pages)

- STK11C88 (15 pages)

- CY7C1231H (12 pages)

- Perform CY7C142 (15 pages)

- CY14E256L (18 pages)

- STK15C88 (15 pages)

- CY7C1297H (15 pages)

- CY7C1441AV33 (31 pages)

- CapSense CY8C20x36 (34 pages)