Cypress CY62137FV30 User Manual

Features, Functional description, Logic block diagram

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document Number: 001-07141 Rev. *F

Revised January 2, 2008

CY62137FV30 MoBL

®

2-Mbit (128K x 16) Static RAM

Features

■

Very high speed: 45 ns

■

Temperature ranges

❐

Industrial: –40°C to +85°C

❐

Automotive-A: –40°C to +85°C

❐

Automotive-E: –40°C to +125°C

■

Wide voltage range: 2.20V–3.60V

■

Pin compatible with CY62137CV/CV25/CV30/CV33,

CY62137V, and CY62137EV30

■

Ultra low standby power

❐

Typical standby current: 1

μA

❐

Maximum standby current: 5

μA (Industrial)

■

Ultra low active power

❐

Typical active current: 1.6 mA at f = 1 MHz (45 ns speed)

■

Easy memory expansion with CE and OE features

■

Automatic power down when deselected

■

CMOS for optimum speed and power

■

Byte power down feature

■

Available in Pb free 48-Ball VFBGA and 44-pin TSOP II

package

Functional Description

The CY62137FV30 is a high performance CMOS static RAM

organized as 128K words by 16 bits. This device features

advanced circuit design to provide ultra low active current. This

is ideal for providing More Battery Life™ (MoBL

®

) in portable

applications such as cellular telephones. The device also has an

automatic power down feature that significantly reduces power

consumption by 90% when addresses are not toggling. Placing

the device into standby mode reduces power consumption by

more than 99% when deselected (CE HIGH or both BLE and

BHE are HIGH). The input and output pins (IO

0

through IO

15

) are

placed in a high impedance state in the following conditions:

■

Deselected (CE HIGH)

■

Outputs are disabled (OE HIGH

■

Both Byte High Enable and Byte Low Enable are disabled

(BHE, BLE HIGH)

■

Write operation is active (CE LOW and WE LOW)

Write to the device by taking Chip Enable (CE) and Write Enable

(WE) inputs LOW. If Byte Low Enable (BLE) is LOW, then data

from IO pins (IO

0

through IO

7

) is written into the location

specified on the address pins (A

0

through A

16

). If Byte High

Enable (BHE) is LOW, then data from IO pins (IO

8

through IO

15

)

is written into the location specified on the address pins (A

0

through A

16

).

Read from the device by taking Chip Enable (CE) and Output

Enable (OE) LOW, while forcing the Write Enable (WE) HIGH. If

Byte Low Enable (BLE) is LOW, then data from the memory

location specified by the address pins appear on IO

0

to IO

7

. If

Byte High Enable (BHE) is LOW, then data from memory

appears on IO

8

to IO

15

. See the

on page 9 for a

complete description of read and write modes.

For best practice recommendations, refer to the Cypress

applicatio

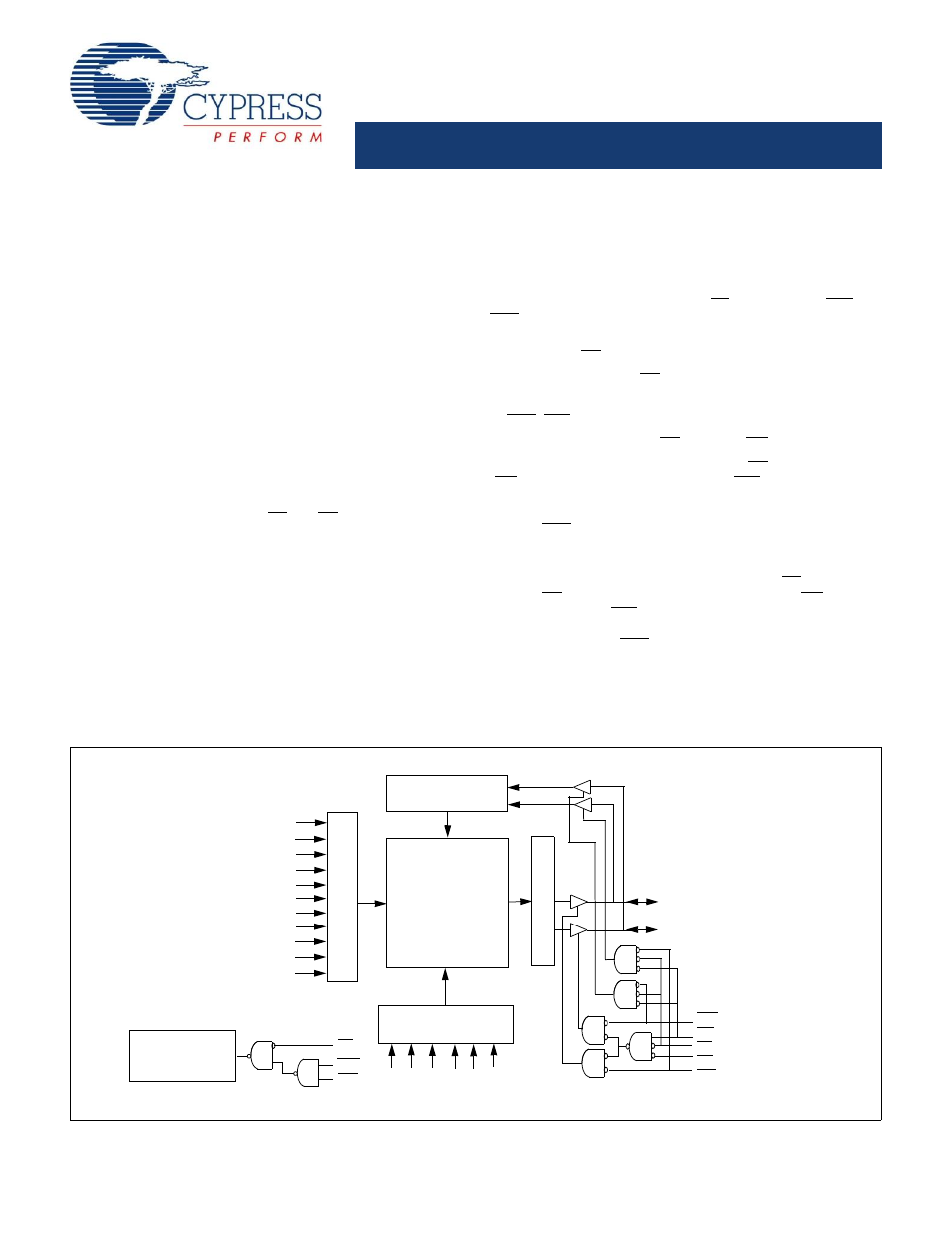

128K x 16

RAM Array

IO

0

–IO

7

ROW D

E

COD

E

R

A

8

A

7

A

6

A

5

A

2

COLUMN DECODER

A

11

A

12

A

13

A

14

A

15

S

E

NS

E AMPS

DATA IN DRIVERS

OE

A

4

A

3

IO

8

–IO

15

CE

WE

BHE

A

16

A

0

A

1

A

9

A

10

BLE

BHE

BLE

CE

POWER DOWN

CIRCUIT

Logic Block Diagram

Document Outline

- Features

- Functional Description

- Logic Block Diagram

- Product Portfolio

- Pin Configuration

- Maximum Ratings

- Operating Range

- Electrical Characteristics

- Capacitance

- Thermal Resistance

- AC Test Loads and Waveforms

- Data Retention Characteristics

- Data Retention Waveform

- Switching Characteristics

- Switching Waveforms

- Truth Table

- Ordering Information

- Package Diagram

- Document History Page