Cypress CY7C1364C User Manual

Page 18

CY7C1364C

Document #: 38-05689 Rev. *E

Page 18 of 18

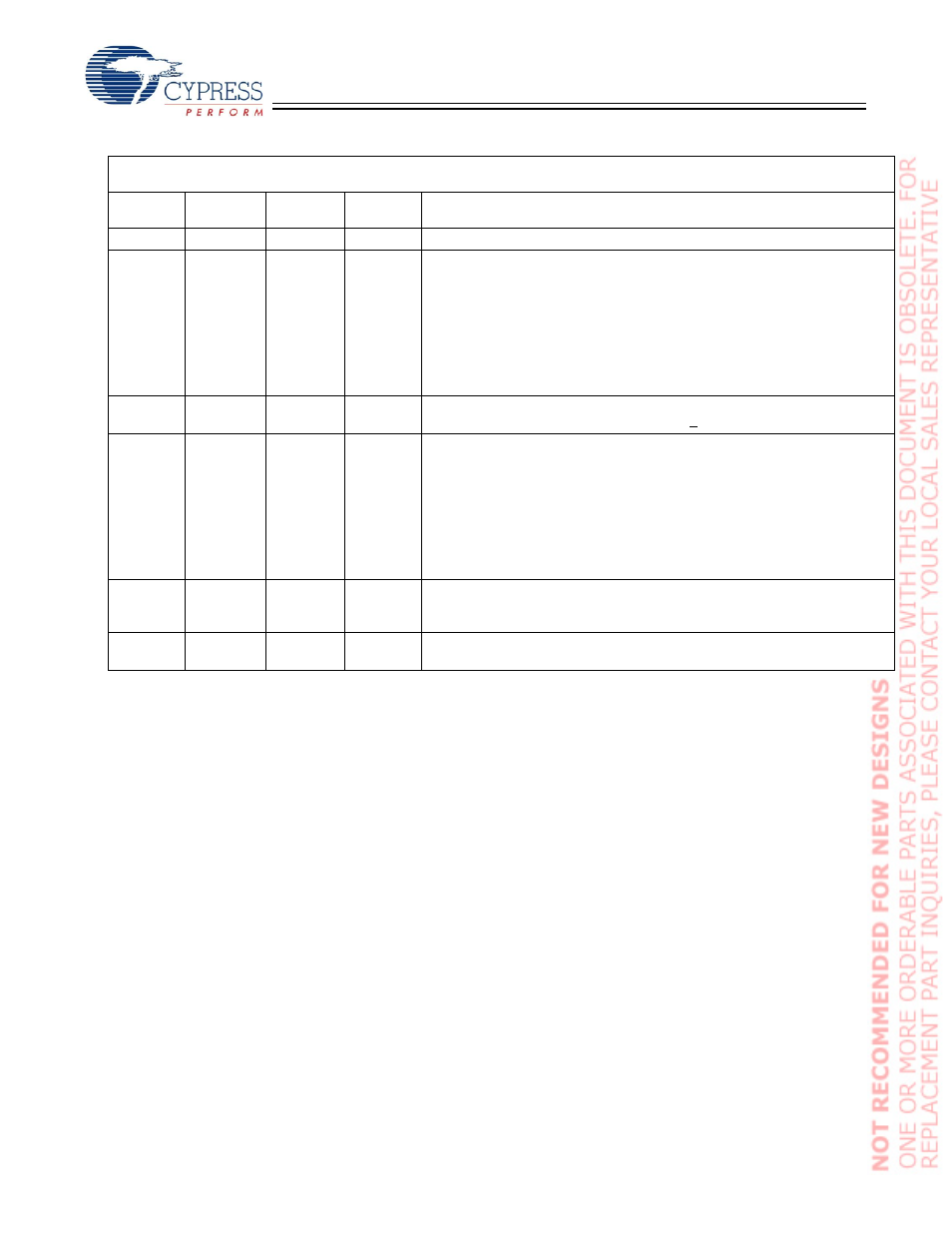

Document History Page

Document Title: CY7C1364C 9-Mbit (256K x 32) Pipelined Sync SRAM

Document Number: 38-05689

REV.

ECN NO.

Issue Date

Orig. of

Change

Description of Change

**

286269

See ECN

PCI

New data sheet

*A

320834

See ECN

PCI

Changed 225 MHz into 250 MHz

Changed

Θ

JA

and

Θ

JC

for TQFP

from 25 and 9

°C/W to 29.41 and 6.13 °C/W

respectively

Modified V

OL,

V

OH

test conditions

Added Industrial Operating Range

Changed Snooze to Sleep in the ZZ Mode Electrical Characteristics

Shaded 250 MHz speed bin in the AC/DC table and Selection Guide

Added AJXC package in the Ordering Information

Updated Ordering Information Table

*B

377095

See ECN

PCI

Changed I

SB2

from 30 to 40 mA

Modified test condition in note# 9 from V

IH

< V

DD

to

V

IH

< V

DD

*C

408725

See ECN

RXU

Changed address of Cypress Semiconductor Corporation on Page# 1 from

“3901 North First Street” to “198 Champion Court”

Changed three-state to tri-state

Converted from Preliminary to Final

Modified “Input Load” to “Input Leakage Current except ZZ and MODE” in the

Electrical Characteristics Table

Replaced Package Name column with Package Diagram in the Ordering

Information table

Updated the ordering information

*D

429278

See ECN

NXR

Added 2.5 V I/O option

Included 2 Chip Enable Pinout

Updated Ordering Information Table

*E

501828

See ECN

VKN

Added the Maximum Rating for Supply Voltage on V

DDQ

Relative to GND

Updated the Ordering Information table.