Cypress CY62138FV30 User Manual

Page 13

Document #: 001-08029 Rev. *E

Page 13 of 13

CY62138FV30 MoBL

®

Document History Page

Document Title: CY62138FV30 MoBL

®

, 2-Mbit (256K x 8) Static RAM

Document Number: 001-08029

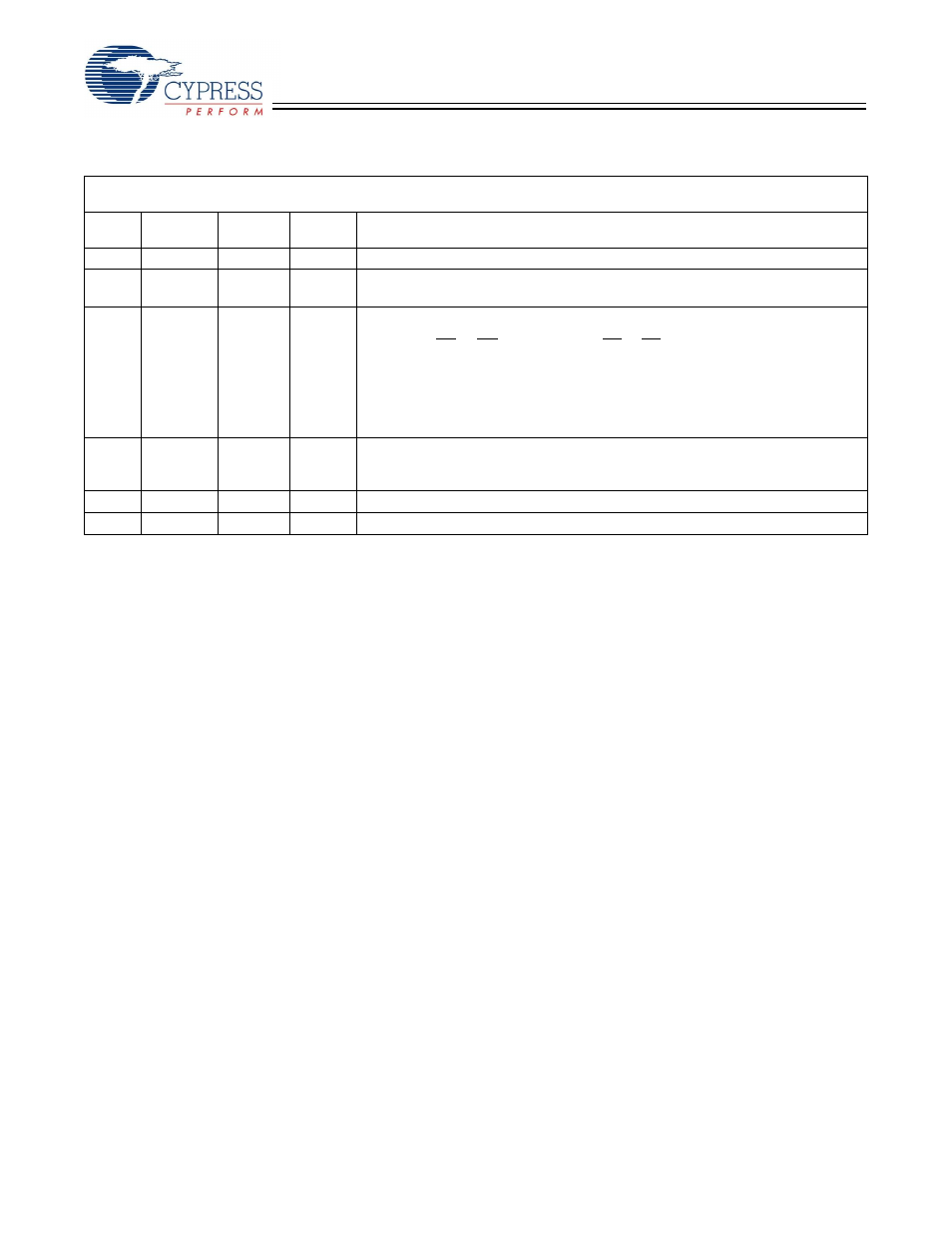

REV.

ECN NO.

Issue

Date

Orig. of

Change

Description of Change

**

463660

See ECN

NXR

New data sheet

*A

467351

See ECN

NXR

Added 32-pin TSOP II package, 32 pin TSOP I and 32 pin STSOP packages

Changed ball A3 from NC to CE

2

in 36-ball FBGA pin out

*B

566724

See ECN

NXR

Converted from Preliminary to Final

Corrected typo in 32 pin TSOP II pin configuration diagram on page #2 (changed

pin 24 from CE

1

to OE and pin 22 from CE to CE

1

)

Changed the I

CC(max)

value from 2.25 mA to 2.5 mA for test condition f=1 MHz

Changed the I

SB2(typ)

value from 0.5

µA to 1 µA

Changed the I

SB2(max)

value from 2.5

µA to 5 µA

Changed the I

CCDR(typ)

value from 0.5

µA to 1 µA and I

CCDR(max)

value from 2.5

µA to 4 µA

*C

797956

See ECN

VKN

Added 32-pin SOIC package

Updated VIL spec for SOIC, TSOP-II, TSOP-I, and STSOP packages on Electrical

characteristics table

*D

809101

See ECN

VKN

Corrected typo in the Ordering Information table

*E

940341

See ECN

VKN

Added footnote #7 related to I

SB2

and

I

CCDR