2 continuous conversion mode, Continuous conversion mode, 1 for – Cirrus Logic CS5530 User Manual

Page 24: Cs5530

CS5530

24

DS742F3

2.5.2 Continuous Conversion Mode

When the user transmits the perform continuous

conversion command, the converter begins contin-

uous conversions using the word rate and polarity

selections set in the configuration register. Once

the command byte is transmitted, the serial port en-

ters data mode where it waits until a conversion is

complete. After the conversion is done, SDO falls

to logic 0 to act as a flag to indicate that the data is

available. Forty SCLKs are then needed to read the

conversion. The first 8 SCLKs are used to clear the

SDO flag. The last 32 SCLKs are needed to read

the conversion result. If ‘00000000’ is provided to

SDI during the first 8 SCLKs when the SDO flag is

cleared, the converter remains in this conversion

mode and continues to convert using the same word

rate and polarity information. In continuous con-

version mode, not every conversion word needs to

be read. The user needs only to read the conversion

words required for the application as SDO rises and

falls to indicate the availability of new conversion

data. Note that if a conversion is not read before the

next conversion data becomes available, it will be

lost and replaced by the new conversion data. To

exit this conversion mode, the user must provide

‘11111111’ to the SDI pin during the first 8 SCLKs

after SDO falls. If the user decides to exit, 32

SCLKs are required to clock out the last conversion

before the converter returns to command mode.

The number of clock cycles a continuous conver-

sion takes for each Output Word Setting is listed in

Table 2. The first conversion from the part in con-

tinuous conversion mode will be longer than the

following conversions due to start-up overhead.

The

±

8 (FRS = 0) or

±

10 (FRS = 1) clock ambigu-

ity is due to internal synchronization between the

SCLK input and the oscillator.

Note:

When changing channels, or after performing

calibrations and/or single conversions, the

user must ignore the first three (for OWRs

less than 3200 Sps, MCLK = 4.9152 MHz) or

first five (for OWR

≥ 3200 Sps) conversions in

continuous conversion mode, as residual

filter coefficients must be flushed from the

filter before accurate conversions are

performed.

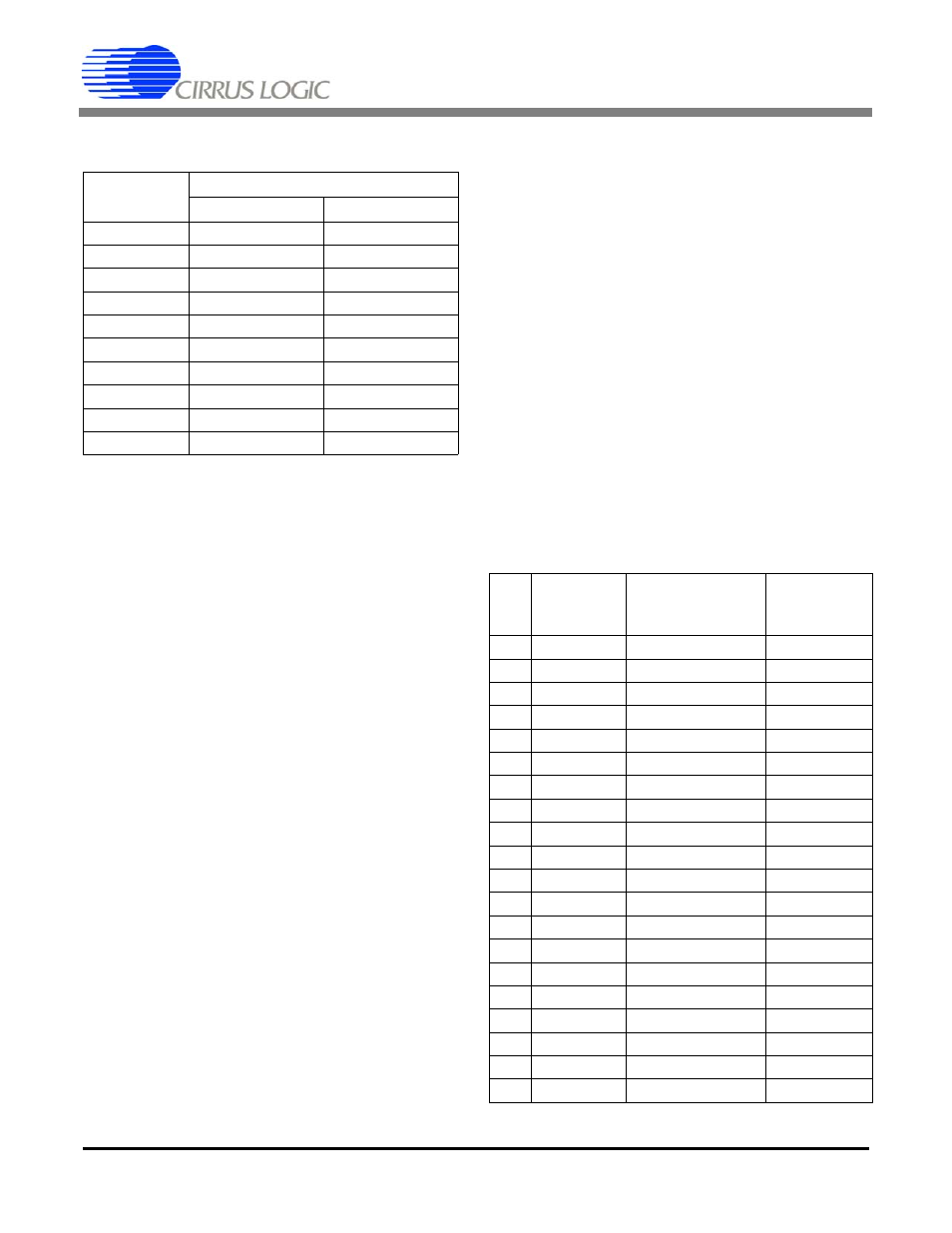

Table 1. Conversion Timing for Single Mode

(WR3-WR0)

Clock Cycles

FRS = 0

FRS = 1

0000

171448 ± 8

205738 ± 10

0001

335288 ± 8

402346 ± 10

0010

662968 ± 8

795562 ± 10

0011

1318328 ± 8

1581994 ± 10

0100

2629048 ± 8

3154858 ± 10

1000

7592 ± 8

9110 ± 10

1001

17848 ± 8

21418 ± 10

1010

28088 ± 8

33706 ± 10

1011

48568 ± 8

58282 ± 10

1100

89528 ± 8

107434 ± 10

Table 2. Conversion Timing for Continuous Mode

FRS (WR3-WR0)

Clock Cycles

(First Conversion)

Clock Cycles

(All Other

Conversions)

0

0000

89528 ± 8

40960

0

0001

171448 ± 8

81920

0

0010

335288 ± 8

163840

0

0011

662968 ± 8

327680

0

0100

1318328 ± 8

655360

0

1000

2472 ± 8

1280

0

1001

12728 ± 8

2560

0

1010

17848 ± 8

5120

0

1011

28088 ± 8

10240

0

1100

48568 ± 8

20480

1

0000

107434 ± 10

49152

1

0001

205738 ± 10

98304

1

0010

402346 ± 10

196608

1

0011

795562 ± 10

393216

1

0100

1581994 ± 10

786432

1

1000

2966 ± 10

1536

1

1001

15274 ± 10

3072

1

1010

21418 ± 10

6144

1

1011

33706 ± 10

12288

1

1100

58282 ± 10

24576