4 performing calibrations, 5 system calibration, 6 calibration tips – Cirrus Logic CS5530 User Manual

Page 22: Cs5530

CS5530

22

DS742F3

2.4.4 Performing Calibrations

To perform a calibration, the user must send a com-

mand byte with its MSB=1, and the appropriate

calibration bits (CC2-CC0) set to choose the type

of calibration to be performed. The calibration will

be performed using the filter rate, and siganl span

(unipolar or bipolar) as set in the configuration reg-

ister. The length of time it takes to do a calibration

is slightly less than the amount of time it takes to do

a single conversion (see Table 1 for single conver-

sion timing). Offset calibration takes 608 clock cy-

cles less than a single conversion when FRS = 0,

and 729 clock cycles less when FRS = 1. Gain cal-

ibration takes 128 clock cycles less than a single

conversion when FRS = 0, and 153 clock cycles

less when FRS = 1.

Once a calibration cycle is complete, SDO falls and

the results are automatically stored in either the

gain or offset register. SDO will remain low until

the next command word is begun. If additional cal-

ibrations are performed while referencing the same

calibration registers, the last calibration results will

replace the effects from the previous calibration.

Only one calibration is performed with each com-

mand byte.

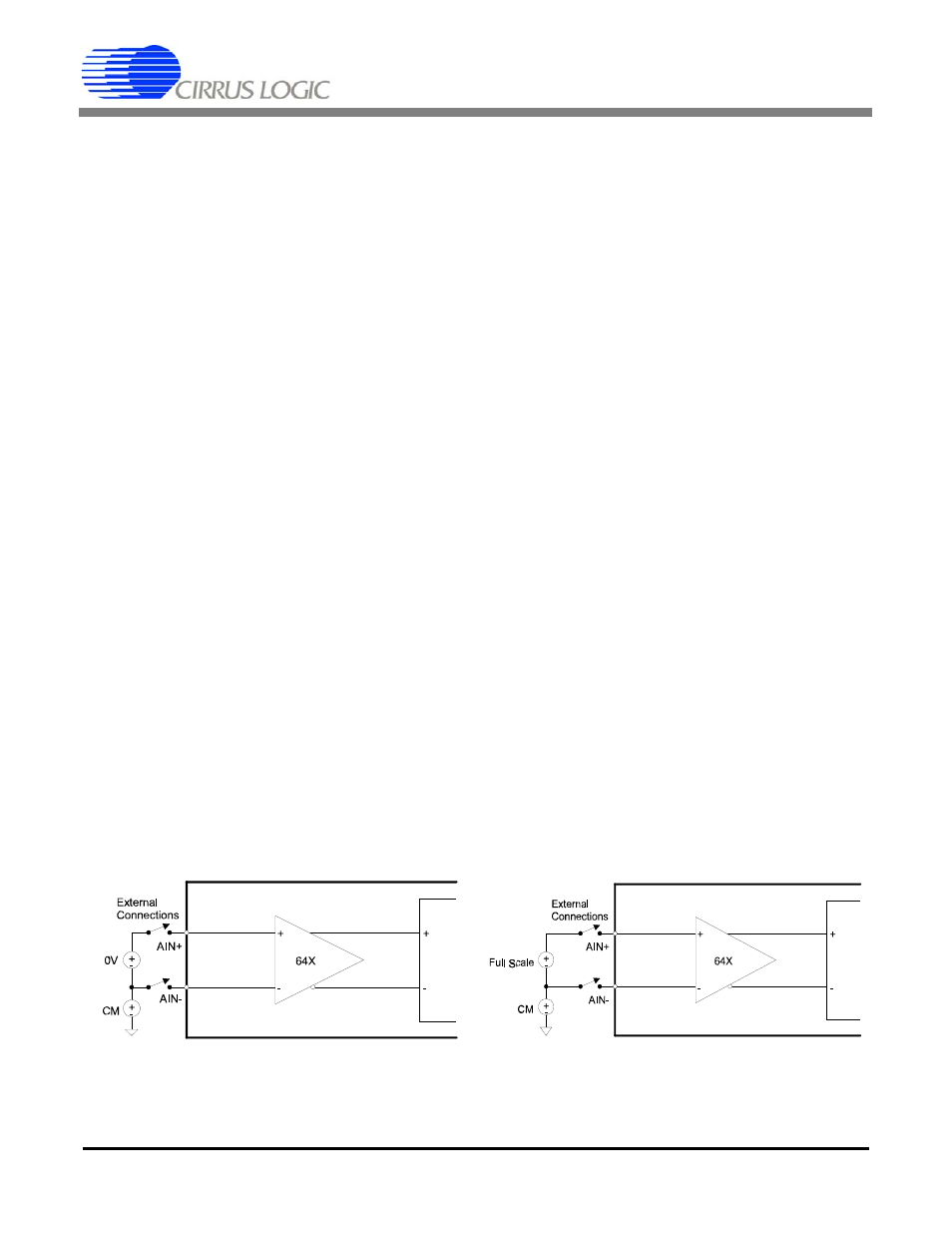

2.4.5 System Calibration

For the system calibration functions, the user must

supply the converter input calibration signals which

represent ground and full-scale. When a system off-

set calibration is performed, a ground referenced sig-

nal must be applied to the converter. Figure 10

illustrates system offset calibration.

As shown in Figure 11, the user must input a signal

representing the positive full-scale point to perform

a system gain calibration. In either case, the cali-

bration signals must be within the specified calibra-

tion limits for each specific calibration step (refer

to the System Calibration Specifications).

2.4.6 Calibration Tips

Calibration steps are performed at the output word

rate selected by the WR3-WR0 bits of the configu-

ration register. To minimize the effects of peak-to-

peak noise on the accuracy of calibration the con-

verter should be calibrated using the slowest word

rate that is acceptable. It is recommended that

word rates of 240 Sps and higher not be used for

calibration.) To minimize digital noise near the de-

vice, the user should wait for each calibration step

to be completed before reading or writing to the se-

rial port. Reading the calibration registers and aver-

aging multiple calibrations together can produce a

more accurate calibration result. Note that access-

ing the ADC’s serial port before a calibration has

finished may result in the loss of synchronization

between the microcontroller and the ADC, and may

prematurely halt the calibration cycle.

Figure 10. System Calibration of Offset

Figure 11. System Calibration of Gain