General description, 1 analog input, General description 2.1 – Cirrus Logic CS5530 User Manual

Page 11: Analog input, Cs5530

CS5530

DS742F3

11

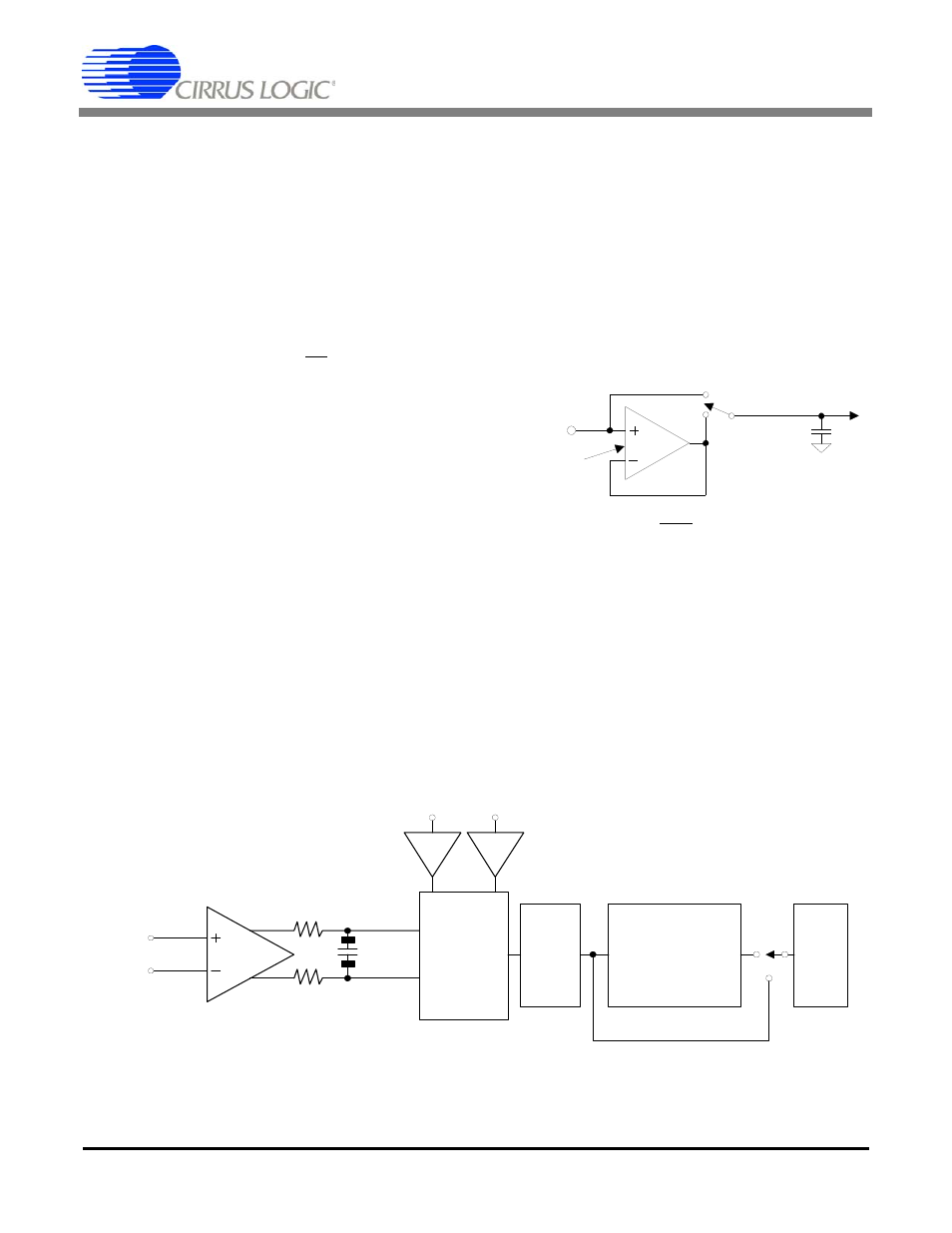

2. GENERAL DESCRIPTION

The CS5530 is a

ΔΣ Analog-to-Digital Converter

(ADC) which uses charge-balance techniques to

achieve 24-bit performance. The ADC is optimized

for measuring low-level unipolar or bipolar signals

in weigh scale, process control, scientific, and med-

ical applications.

To accommodate these applications, the ADC in-

cludes a very-low-noise, chopper-stabilized instru-

mentation amplifier (12 nV/

√Hz @ 0.1 Hz) with a

gain of 64X. This ADC also includes a fourth-order

ΔΣ modulator followed by a digital filter which pro-

vides twenty selectable output word rates of 6.25,

7.5, 12.5, 15, 25, 30, 50, 60, 100, 120, 200, 240, 400,

480, 800, 960, 1600, 1920, 3200, and 3840 samples

per second (MCLK = 4.9152 MHz).

To ease communication between the ADCs and a

micro-controller, the converters include a simple

three-wire serial interface which is SPI and Mi-

crowire compatible with a Schmitt-trigger input on

the serial clock (SCLK).

2.1 Analog Input

Figure 3 illustrates a block diagram of the CS5530.

The front end includes a chopper-stabilized instru-

mentation amplifier with a gain of 64X.

The amplifier is chopper-stabilized and operates with

a chop clock frequency of MCLK/128. The CVF

(sampling) current into the instrumentation amplifier

is typically 1200 pA over -40°C to +85°C

(MCLK=4.9152 MHz). The common-mode plus sig-

nal range of the instrumentation amplifier is (VA-) +

1.6 V to (VA+) - 1.6 V.

illustrates the input model for the 64X am-

plifier.

Note:

The C = 3.9 pF capacitor is for input current

modeling only. For physical input capacitance

see ‘Input Capacitance’ specification under

Analog Characteristics.

VREF+

Sinc

Digital

Filter

64x

AIN+

AIN-

X1

VREF-

X1

Differential

4 Order

ΔΣ

Modulator

th

5

Programmable

Sinc

Digital Filter

3

Serial

Port

1000

Ω

1000

Ω

22 nF

C1 PIN

C2 PIN

Figure 3. Front End Configuration

AIN

C = 3 .9 pF

f =

V

≤ 8 mV

i = fV C

os

os

n

MCLK

128

Figure 4. Input Model for AIN+ and AIN- Pins