5 output latch pins, 6 filter rate select, 7 word rate select – Cirrus Logic CS5530 User Manual

Page 18: 8 unipolar/bipolar select, 9 open circuit detect, Cs5530

CS5530

18

DS742F3

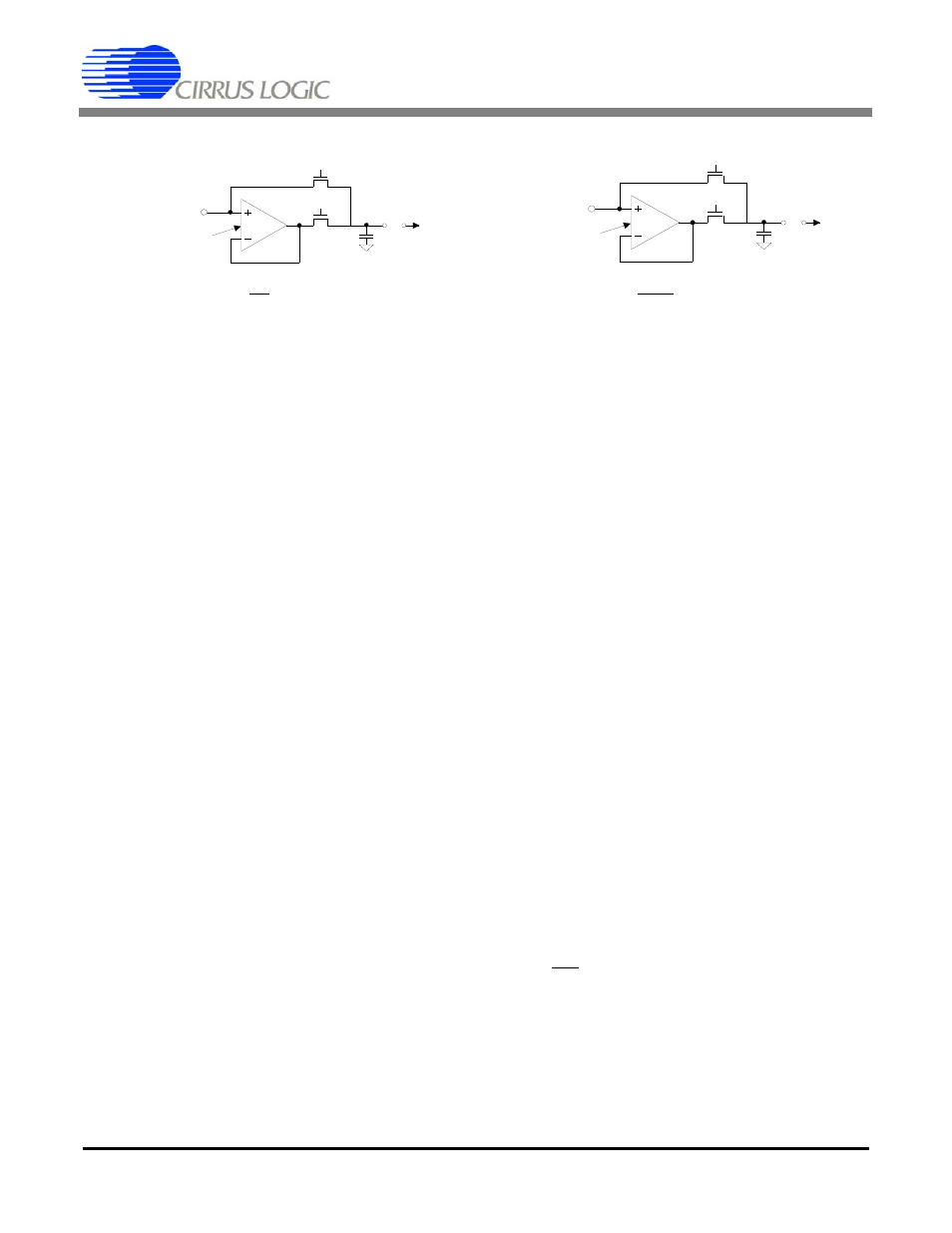

the magnitude of the reference voltage to achieve

optimal performance. Figures 8 and 9 model the ef-

fects on the reference’s input impedance and input

current for each VRS setting. As the models show,

the reference includes a coarse/fine charge buffer

which reduces the dynamic current demand of the

external reference.

The reference’s input buffer is designed to accom-

modate rail-to-rail (common-mode plus signal) in-

put voltages. The differential voltage between the

VREF+ and VREF- can be any voltage from 1.0 V

up to the analog supply (depending on how VRS is

configured), however, the VREF+ cannot go above

VA+ and the VREF- pin can not go below VA-.

Note that the power supplies to the chip should be

established before the reference voltage.

2.3.5 Output Latch Pins

The A1-A0 pins of the ADC mimic the D24-D23

bits of the configuration register. A1-A0 can be

used to control external multiplexers and other log-

ic functions outside the converter. The A1-A0 out-

puts can sink or source at least 1 mA, but it is

recommended to limit drive currents to less than

20

μA to reduce self-heating of the chip. These out-

puts are powered from VA+ and VA-. Their output

voltage will be limited to the VA+ voltage for a

logic 1 and VA- for a logic 0. Note that if the latch

bits are used to modify the analog input signal the

user should delay performing a conversion until he

knows the effects of the A0/A1 bits are fully set-

tled.

2.3.6 Filter Rate Select

The Filter Rate Select bit (FRS) modifies the output

word rates of the converter to allow either 50 Hz or

60 Hz rejection when operating from a 4.9152

MHz crystal. If FRS is cleared to logic 0, the word

rates and corresponding filter characteristics can be

selected using the Configuration Register. Rates

can be 7.5, 15, 30, 60, 120, 240, 480, 960, 1920, or

3840 Sps when using a 4.9152 MHz clock. If FRS

is set to logic 1, the word rates and corresponding

filter characteristics scale by a factor of 5/6, mak-

ing the selectable word rates 6.25, 12.5, 25, 50,

100, 200, 400, 800, 1600, and 3200 Sps when using

a 4.9152 MHz clock. When using other clock fre-

quencies, these selectable word rates will scale lin-

early with the clock frequency that is used.

2.3.7 Word Rate Select

The Word Rate Select bits (WR3-WR0) allow slec-

tion of the output word rate of the converter as de-

picted in the Configuration Register Descriptions.

The word rate chosen by the WR3-WR0 bits is

modified by the setting of the FRS bit as presented

in the previous paragraph.

2.3.8 Unipolar/Bipolar Select

The UP/BP Select bit sets the converter to measure

either a unipolar or bipolar input span.

2.3.9 Open Circuit Detect

When the OCD bit is set it activates a current

source as a means to test for open thermocouples.

VREF

C = 14pF

f =

2

φ Fine

1

V

≤ 8 mV

i = fV

C

os

os

n

φ Coarse

MCLK

16

VRS = 1; 1 V

≤ V

≤ 2.5 V

REF

Figure 8. Input Reference Model when VRS = 1

VREF

C = 7 pF

f =

2

φ Fine

1

V

≤ 16 mV

i = fV

C

os

os

n

φ Coarse

MCLK

16

VRS = 0; 2.5 V < V

≤

VA+

REF

Figure 9. Input Reference Model when VRS = 0