Cirrus Logic CS5530 User Manual

Ultra-low-noise amplifier, With, Features & description

Copyright

Cirrus Logic, Inc. 2009

(All Rights Reserved)

http://www.cirrus.com

CS5530

24-bit ADC

with

Ultra-low-noise Amplifier

Features

& Description

Chopper-stabilized Instrumentation

Amplifier, 64X

• 12 nV/

√Hz @ 0.1 Hz (No 1/f noise)

• 1200 pA Input Current

Digital Gain Scaling up to 40x

Delta-sigma Analog-to-digital Converter

• Linearity Error: 0.0015% FS

• Noise Free Resolution: Up to 19 bits

Scalable V

REF

Input: Up to Analog Supply

Simple Three-wire Serial Interface

• SPI™ and Microwire™ Compatible

• Schmitt-trigger on Serial Clock (SCLK)

Onboard Offset and Gain Calibration

Registers

Selectable Word Rates: 6.25 to 3,840 Sps

Selectable 50 or 60 Hz Rejection

Power Supply Configurations

• VA+ = +5 V; VA- = 0 V; VD+ = +3 V to +5 V

• VA+ = +2.5 V; VA- = -2.5 V; VD+ = +3 V to +5 V

• VA+ = +3 V; VA- = -3 V; VD+ = +3 V

General Description

The CS5530 is a highly integrated

ΔΣ Analog-to-Digital

Converter (ADC) which uses charge-balance techniques

to achieve 24-bit performance. The ADC is optimized for

measuring low-level unipolar or bipolar signals in weigh

scale, process control, scientific, and medical

applications.

To accommodate these applications, the ADC includes

a very-low-noise, chopper-stabilized instrumentation

amplifier (12 nV/

√Hz @ 0.1 Hz) with a gain of 64X. This

device also includes a fourth-order

ΔΣ modulator fol-

lowed by a digital filter which provides twenty selectable

output word rates of 6.25, 7.5, 12.5, 15, 25, 30, 50, 60, 100,

120, 200, 240, 400, 480, 800, 960, 1600, 1920, 3200, and

3840 Sps (MCLK = 4.9152 MHz).

To ease communication between the ADC and a micro-

controller, the converter includes a simple three-wire se-

rial interface which is SPI and Microwire compatible with

a Schmitt-trigger input on the serial clock (SCLK).

High dynamic range, programmable output rates, and

flexible power supply options make this device an ideal

solution for weigh scale and process control

applications.

ORDERING INFORMATION

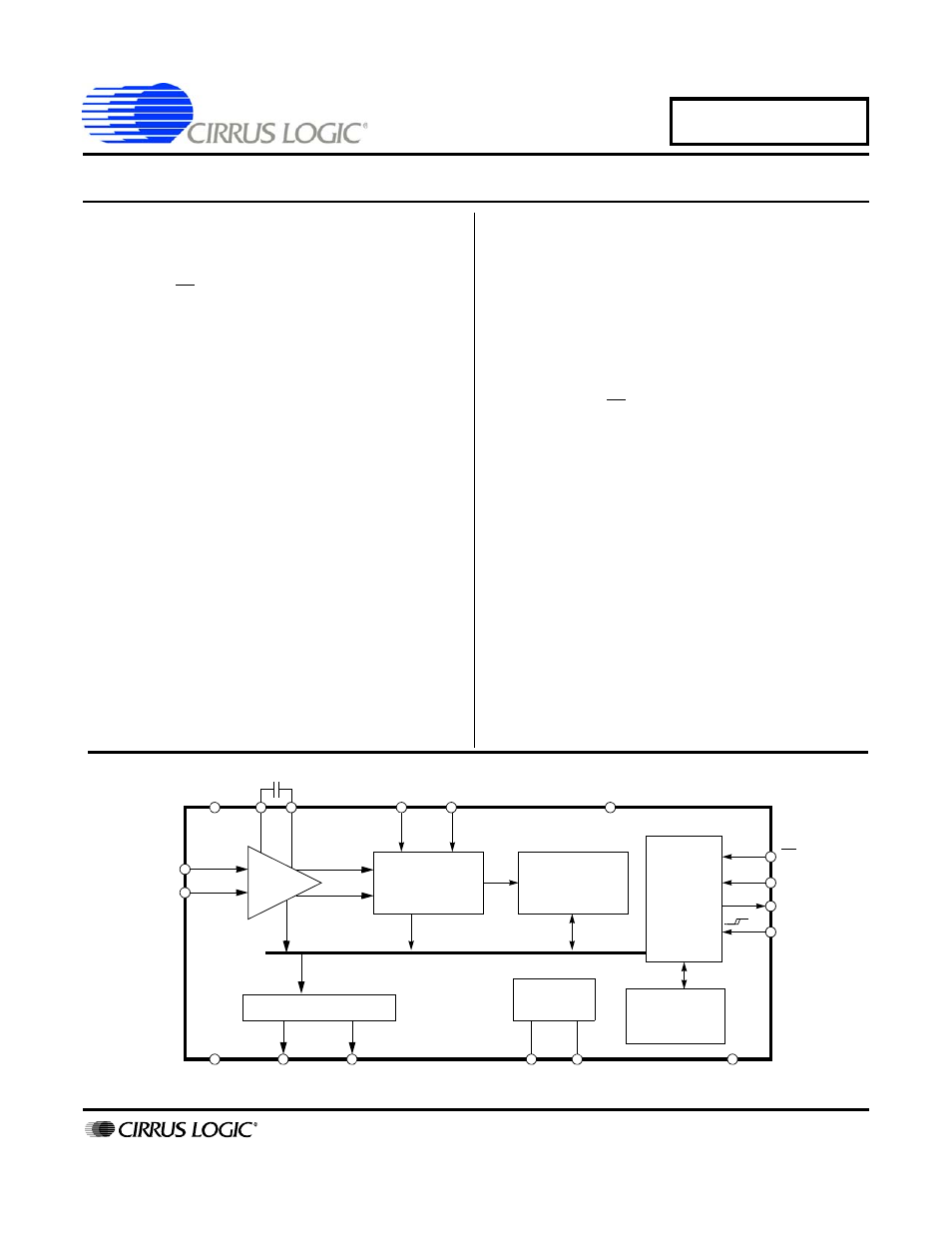

VA+

C1

C2

VREF+

VREF-

VD+

DIFFERENTIAL

4

TH

ORDER

ΔΣ

MODULATOR

PROGRAMMABLE

SINC FIR FILTER

AIN1+

AIN1-

SERIAL

INTERFACE

LATCH

CLOCK

GENERATOR

CALIBRATION

SRAM/CONTROL

LOGIC

DGND

CS

SDI

SDO

SCLK

OSC2

OSC1

A1

A0

VA-

64X

NOV ‘09

DS742F3

Document Outline

- Features & Description

- Table of Contents

- List of Figures

- List of Tables

- 1. Characteristics And Specifications

- 2. General Description

- 2.1 Analog Input

- 2.2 Overview of ADC Register Structure and Operating Modes

- 2.3 Configuration Register

- 2.4 Calibration

- 2.5 Performing Conversions

- 2.6 Using Multiple ADCs Synchronously

- 2.7 Conversion Output Coding

- 2.8 Digital Filter

- 2.9 Clock Generator

- 2.10 Power Supply Arrangements

- 2.11 Getting Started

- 2.12 PCB Layout

- 3. Pin Descriptions

- 4. Specification Definitions

- 5. Package Drawings

- 6. Ordering Information

- 7. Environmental, Manufacturing, & Handling Information