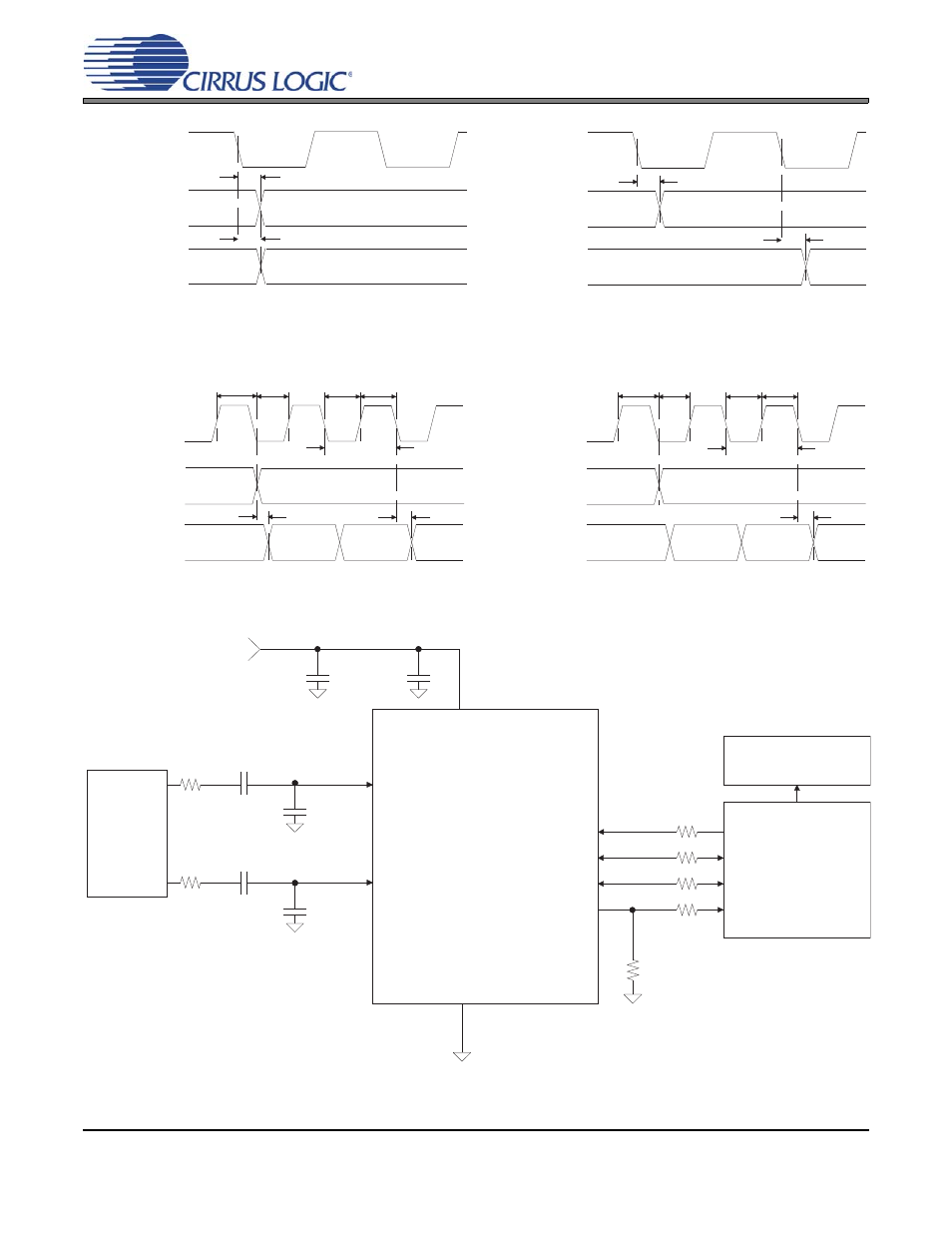

Figure 1. typical connection diagram, Typical connection diagram – Cirrus Logic CS5331A User Manual

Page 8

8

DS138F6

CS5330A/31A

SCLK output

SDATA

t sdo

LRCK output

t mslr

SCLK to SDATA LRCK - MASTER mode (CS5330A)

SCLK output

tmslr

SDATA

tsdo

LRCK output

SCLK to SDATA LRCK - MASTER mode (CS5331A)

SDATA

SCLK input

(SLAVE mode)

(SLAVE mode)

LRCK input

sclkh

t

dss

t

MSB MSB-1

sclkl

t

slr1

t

slr2

t

t

sclkw

SCLK to LRCK & SDATA - SLAVE mode (CS5331A)

SDATA

SCLK input

(SLAVE mode)

(SLAVE mode)

LRCK input

sclkh

t

dss

t

MSB

MSB-1 MSB-2

lrdss

t

sclkl

t

slr1

t

slr2

t

t

sclkw

SCLK to LRCK & SDATA - SLAVE mode (CS5330A)

Analog

Input

Circuits

10

μ

F

VA+

AGND

+5V

Analog

AINL

AINR

+

0.1

μ

F

CS5330A

CS5331A

LRCK

MCLK

SCLK

150

Ω

SDATA

47 k

Ω

*

*

**

8

5

7

4

2

3

1

6

.01

μ

F

150

Ω

**

.01

μ

F

1 k

Ω

1 k

Ω

1 k

Ω

1 k

Ω

**

.47

μ

F

.47

μ

F

Required for Master mode only

Optional if analog input circuits biased

to within ± 5% of CS5330A/CS5331A

nominal input bias voltage

Audio Data

Processor

Timing

Logic

&

Clock

Figure 1. Typical Connection Diagram