Hardware functional description, 1 dsp core, 1 dsp memory – Cirrus Logic CS48AU2B User Manual

Page 7: 2 dma controller, Table 2. device and firmware selection guide, Confidenti a l dra ft delp hi

CS48AU2B Data Sheet

Dedicated 32-bit Audio DSP for Audyssey Laboratories Technology

DS876F3

Copyright 2009 Cirrus Logic

7

CONFIDENTIAL

CONFIDENTI

A

L

DRA

FT

DELP

HI

4. Hardware Functional Description

4.1 DSP Core

The CS48AU2B DSP is a single-core DSP with separate X and Y data and P code memory spaces.

The DSP core is a high-performance, 32-bit, fully user-programmable, fixed-point DSP that is

capable of performing two multiply-and-accumulate (MAC) operations per clock cycle. The DSP core

has eight 72-bit accumulators, four X- and four Y-data registers, and 12 index registers.

The DSP core is coupled to a flexible DMA engine. The DMA engine can move data between

peripherals such as the serial control port (SCP), digital audio input (DAI) and digital audio output

(DAO), or any DSP core memory, all without the intervention of the DSP. The DMA engine off loads

data move instructions from the DSP core, leaving more MIPS available for signal processing

instructions.

CS48AU2B functionality is controlled by DSP firmware or application codes that are downloaded to

the CS48AU2B from a host controller or external serial FLASH/EEPROM.

Users can develop their applications using DSP Composer to create the processing chain and then

compile the image into a series of commands that are sent to the CS48AU2B through the SCP. The

processing application can either load modules (matrix-processors, virtualizers, post-processors)

from the DSPs on-board ROM, or custom firmware can be downloaded through the SCP.

4.1.1 DSP Memory

The DSP core has its own on-chip data and program RAM and ROM and does not require external

memory for post-processing applications.

The Y-RAM and P-RAM share a single block of memory that can be configured to make Y and P

equal in size, or more memory can be allocated for Y-RAM in 2kword blocks.

4.1.2 DMA Controller

The powerful 8-channel DMA controller can move data between 8 on-chip resources. Each resource

has its own arbiter: X, Y, and P RAMs/ROMs and the peripheral bus. Modulo and linear addressing

modes are supported, with flexible start address and increment controls. The service intervals for

each DMA channel, as well as up to 6 interrupt events, are programmable.

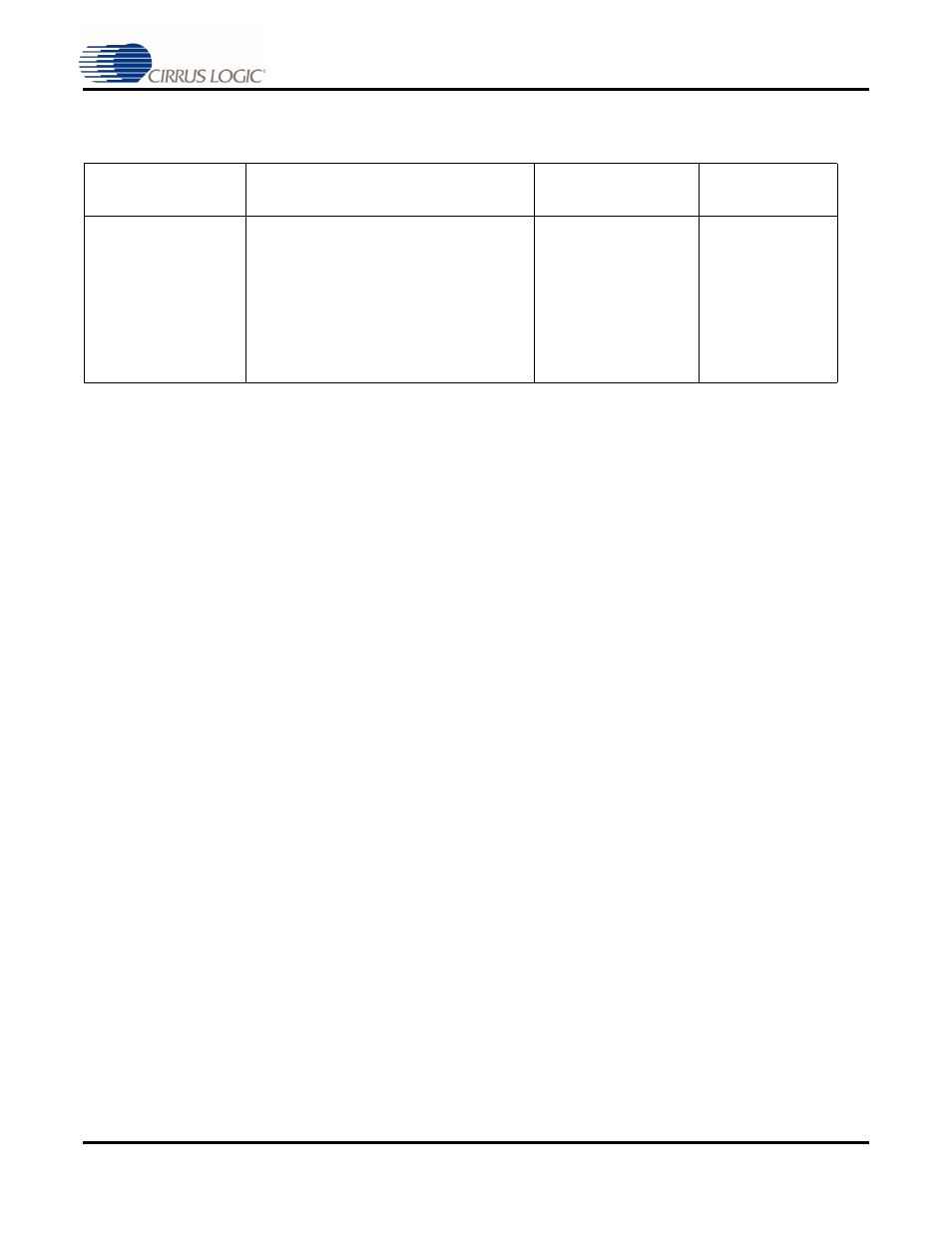

Table 2. Device and Firmware Selection Guide

Device

Suggested

Application

Channel Count

Input/Output

Package

CS48AU2B-CQZ

Digital TV

Portable Audio Docking Station

Portable DVD

DVD Mini / Receiver

Multimedia PC Speakers

8 Channel Car Audio

DVD Receiver

High-end Digital TV

12 channel Car Audio

Up to 12 channel in /12

channel out

48-pin QFP