Cirrus Logic CS485xx User Manual

Cs485xx, Cs485xx family data sheet, Features

Copyright

Cirrus Logic, Inc. 2011

(All Rights Reserved)

DS734F5

OCT '11

CS485xx Family Data Sheet

Features

Cost-effective, High-performance 32-bit DSP

300,000,000 MAC/S (multiply accumulates per second)

Dual MAC cycles per clock

72-bit accumulators are the most accurate in the industry

24k x 32 SRAM, 2k blocks - assignable to data or program

Internal ROM contains a variety of configurable sound

enhancement feature sets

8-channel internal DMA

Internal watch-dog DSP lock-up prevention

DSP Tool Set w/ Private Keys for Protecting Customer IP

Configurable Serial Audio Inputs/Outputs

Configurable for all input/output types

Maximum 32-bit @ 192 kHz

Supports 32-bit audio sample I/O between DSP chips

TDM input modes (multiple channels on same line)

192 kHz SPDIF transmitter

Multi-channel DSD direct stream digital SACD input

Supports Two Different Input Fs Sample Rates

Output can be master or slave

Dual processing path capability

Input supports dual domain slave clocking

Hardware assist time sampling for sample rate conversion

Integrated Clock Manager/PLL

Can operate from external crystal, external oscillator

Input Fs Auto Detection

Host & Boot via Serial Interface

Configurable GPIOs and External Interrupt Input

1.8V Core and a 3.3V I/O that is tolerant to 5V input

Low-power Mode

“Energy Star

®

Ready” in low-power mode, 268 µW in standby

Differentiating from the legacy Cirrus multi-standard, multi-channel

decoders, this new CS485xx family is still based on the same

high-performance 32-bit fixed point Digital Signal Processor core

but instead is equipped with much less memory, tailoring it for more

cost-effective applications associated with multi-channel and

virtual-channel sound enhancements. Target applications are:

Digital Televisions

Multimedia Peripherals

iPod

®

Docking Stations

Automotive Head Units

Automotive Outboard Amplifiers

HD-DVD

™

and Blu-ray Disc

®

DVD Receivers

PC Speakers

There are also a wide variety of licensable DSP codes available

today as seen by the following examples:

Cirrus also has developed, or is developing their own royalty-free

versions of popular features sets like Cirrus Bass Manager, Cirrus

Dynamic Volume Leveler, Cirrus Original Multichannel Surround,

Cirrus Virtual Speaker & Cirrus 3D-Audio.

The CS485xx family is programmed using the Cirrus proprietary

DSP Composer

™

GUI development tool. Processing chains may be

designed using a drag-and-drop interface to place/utilize functional

macro audio DSP primitives. The end result is a software image that

is down-loaded to the DSP via serial host or serial boot modes.

See

for ordering information.

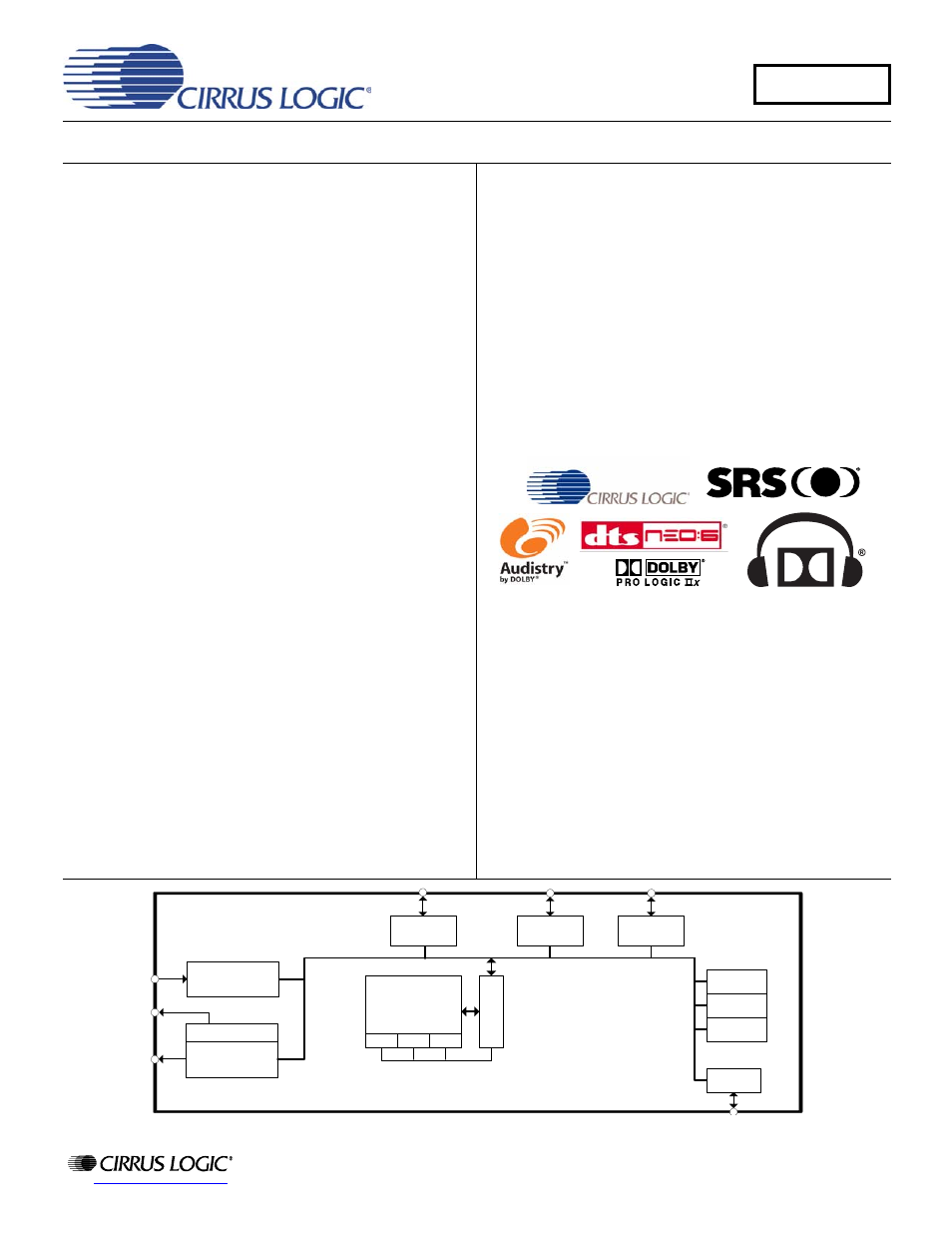

CS485xx Block Diagram

32-bit

DSP

D

M

A

P

X

Y

Serial

Control 1

12 Ch PCM

Audio Out

GPIO

Debug

Watchdog

TMR1

TMR2

PLL

S/PDIF

12 Ch. Audio In /

6 Ch. SACD In

CS485xx

Document Outline

- 1 Documentation Strategy

- 2 Overview

- 3 Code Overlays

- 4 Hardware Functional Description

- 5 Characteristics and Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operations Conditions

- 5.3 Digital DC Characteristics

- 5.4 Power Supply Characteristics

- 5.5 Thermal Data (48-pin LQFP)

- 5.6 Switching Characteristics-RESET

- 5.7 Switching Characteristics-XTI

- 5.8 Switching Characteristics-Internal Clock

- 5.9 Switching Characteristics-Serial Control Port-SPI Slave Mode

- 5.10 Switching Characteristics-Serial Control Port-SPI Master Mode

- 5.11 Switching Characteristics-Serial Control Port-I2C Slave Mode

- 5.12 Switching Characteristics-Serial Control Port-I2C Master Mode

- 5.13 Switching Characteristics-Digital Audio Slave Input Port

- 5.14 Switching Characteristics-DSD Slave Input Port

- 5.15 Switching Characteristics-Digital Audio Output (DAO) Port

- 6 Ordering Information

- 7 Environmental, Manufacturing, and Handling Information

- 8 Device Pinout Diagrams

- 9 Package Mechanical Drawings

- 10 Revision History