3 clock generation, Additional features – Cirrus Logic CS44800 User Manual

Page 24

24

DS632F1

CS44800

•

Digital volume control with soft ramp.

•

Individual channel volume gain, attenuation and mute capability; +24 to -127 dB in 0.25 dB steps.

•

Master volume attenuation; +24 to -127 dB in 0.25 dB steps.

•

Peak Detect and Volume Limiter with programmable attack and release rates.

•

Signal-clipping interrupt indicator.

Additional Features

•

Contains a two-stage digital output filter for speaker impedance compensation.

•

Provides 7 programmable GPIO pins with interrupt generation for easily interfacing to a variety of com-

monly available power state parts. Interrupts can be masked.

•

Selectable over-sample rate for increased audio bandwidth.

•

Power supply clock output, PS_SYNC, with programmable divider

4.3

Clock Generation

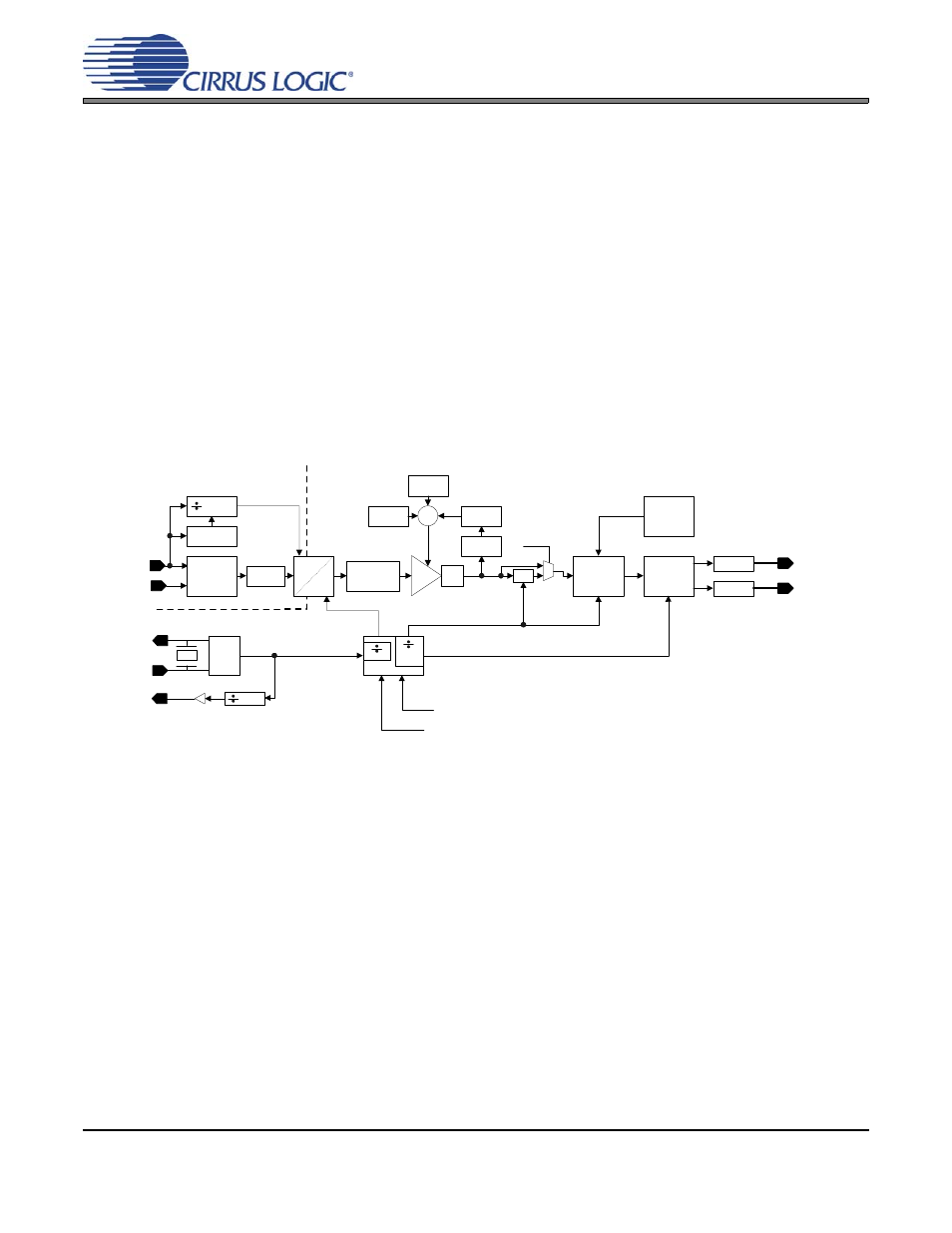

The sources for internal clock generation for the PWM processing are as follows:

•

FsIn Domain:

–

DAI_MCLK, minimum 128Fs

•

FsOut Domain:

–

XTI/XTO (Fundamental or 3

rd

overtone crystal), or

–

Clock signal on XTI (VDX is used to set logic voltage level)

DAI_SCLK

DAI_SDINx

Digital Audio

Input Port

DAI_MCLK

DAI_LRCK

Ratio Detect

SYS_CLK

XTI

XTO

PWM Engine

VO

L

mute

PEAK

DETECT

SRC

2-pole Load

Compensation

Filter

128Fs

LIMITER

Multibit

Σ∆

Modulator

Σ

Master

Volume

Channel

Volume

x2

Over Sample

(OSRATE)

Delay

Delay

XTAL /

CLKIN

1,2,4,8

Clock Control

PWM_MCLK

MOD_MCLK

SRC_MCLK (128Fs)

PSR

Feedback

PWM_OUT+

PWM_OUT-

FsIn FsOut

1, 1.5, 2,

3, 4, 6, 8

AM Freq. Hop

(AM_FREQ_HOP)

2.25

1,1.5,

2,4

Over Sample

(OSRATE)

De-

Emphasis

Figure 13. CS44800 Data Flow Diagram (Single Channel Shown)