5 audio word length, 6 interface control 2 (address 07h), 1 sclk equals mclk – Cirrus Logic CS43L22 User Manual

Page 41: 2 speaker/headphone switch invert, P 41, E awl[1:0] bits, Audio word length” on

DS792F2

41

CS43L22

Confidential Draft

3/4/10

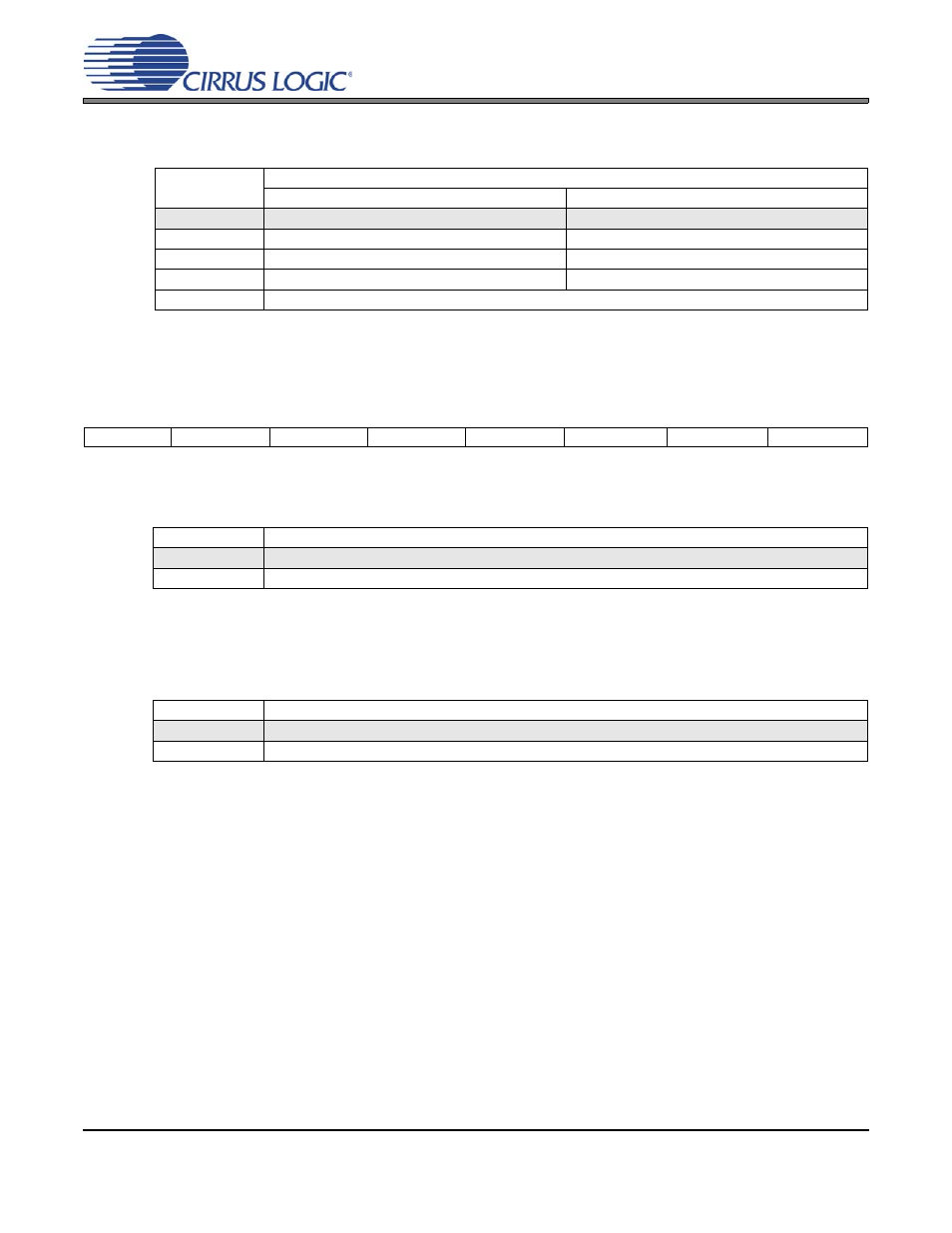

7.5.5

Audio Word Length

Configures the audio sample word length used for the data into SDIN.

Note:

When the internal MCLK/LRCK ratio is set to 125 in Master Mode, the 32-bit data width option

for DSP Mode is not valid unless SCLK=MCLK.

7.6

Interface Control 2 (Address 07h)

7.6.1

SCLK equals MCLK

Configures the SCLK signal source for Master Mode.

Note:

This bit is only valid for MCLK = 12.0000 MHz.

7.6.2

Speaker/Headphone Switch Invert

Determines the control signal polarity of the SPK/HP_SW pin.

AWL[1:0]

Audio Word Length

DSP Mode

Right Justified

00

32-bit data

24-bit data

01

24-bit data

20-bit data

10

20-bit data

18-bit data

11

16-bit data

16-bit data

Application:

7

6

5

4

3

2

1

0

Reserved

SCLK=MCLK

Reserved

Reserved

INV_SWCH

Reserved

Reserved

Reserved

SCLK=MCLK

Output SCLK

0

Re-timed signal, synchronously derived from MCLK

1

Non-retimed, MCLK signal

INV_SWCH

SPK/HP_SW pin 6 Control

0

Not inverted

1

Inverted