2 speed mode, 3 32khz sample rate group, 4 27 mhz video clock – Cirrus Logic CS43L22 User Manual

Page 39: 5 internal mclk/lrck ratio, E videoclk bit, 27 mhz video clock” on

DS792F2

39

CS43L22

Confidential Draft

3/4/10

7.4.2

Speed Mode

Configures the speed mode of the DAC in Slave Mode and sets the appropriate MCLK divide ratio for

LRCK and SCLK in Master Mode.

Notes:

1.

Slave/Master Mode is determined by the M/S bit in

“Master/Slave Mode” on page 40

2.

Certain sample and MCLK frequencies require setting the SPEED[1:0] bits, the 32k_GROUP bit

(

“32kHz Sample Rate Group” on page 39

) and/or the VIDEOCLK bit (

) and RATIO[1:0] bits (

“Internal MCLK/LRCK Ratio” on page 39

). Low sample rates may also

affect dynamic range performance in the typical audio band. Refer to the referenced application for

more information.

3.

These bits are ignored when the AUTO bit (

) is enabled.

7.4.3

32kHz Sample Rate Group

Specifies whether or not the input/output sample rate is 8 kHz, 16 kHz or 32 kHz.

7.4.4

27 MHz Video Clock

Specifies whether or not the external MCLK frequency is 27 MHz

7.4.5

Internal MCLK/LRCK Ratio

Configures the internal MCLK/LRCK ratio.

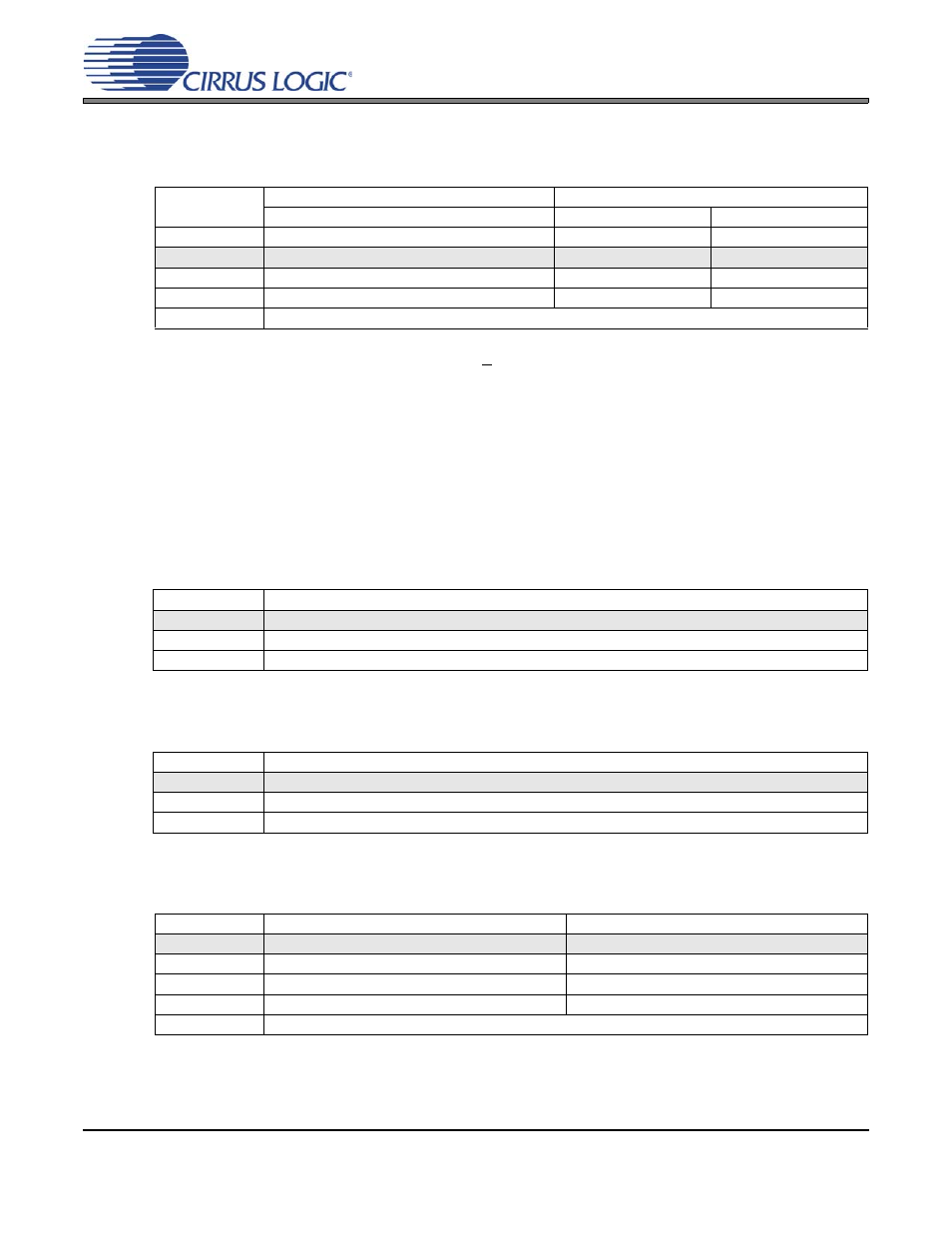

SPEED[1:0]

Slave Mode

Master Mode

Serial Port Speed

MCLK/LRCK Ratio

SCLK/LRCK Ratio

00

Double-Speed Mode (DSM - 50 kHz -100 kHz Fs)

512

64

01

Single-Speed Mode (SSM - 4 kHz -50 kHz Fs)

256

64

10

Half-Speed Mode (HSM - 12.5kHz -25 kHz Fs)

128

64

11

Quarter-Speed Mode (QSM - 4 kHz -12.5 kHz Fs)

128

64

Application:

“Serial Port Clocking” on page 29

32kGROUP

8 kHz, 16 kHz or 32 kHz sample rate?

0

No

1

Yes

Application:

“Serial Port Clocking” on page 29

VIDEOCLK

27 MHz MCLK?

0

No

1

Yes

Application:

“Serial Port Clocking” on page 29

RATIO[1:0]

Internal MCLK Cycles per LRCK

SCLK/LRCK Ratio in Master Mode

00

128

64

01

125

62

10

132

66

11

136

68

Application: