6 serial port clocking, Serial port clock – Cirrus Logic CS43L22 User Manual

Page 29

DS792F2

29

CS43L22

Confidential Draft

3/4/10

4.6

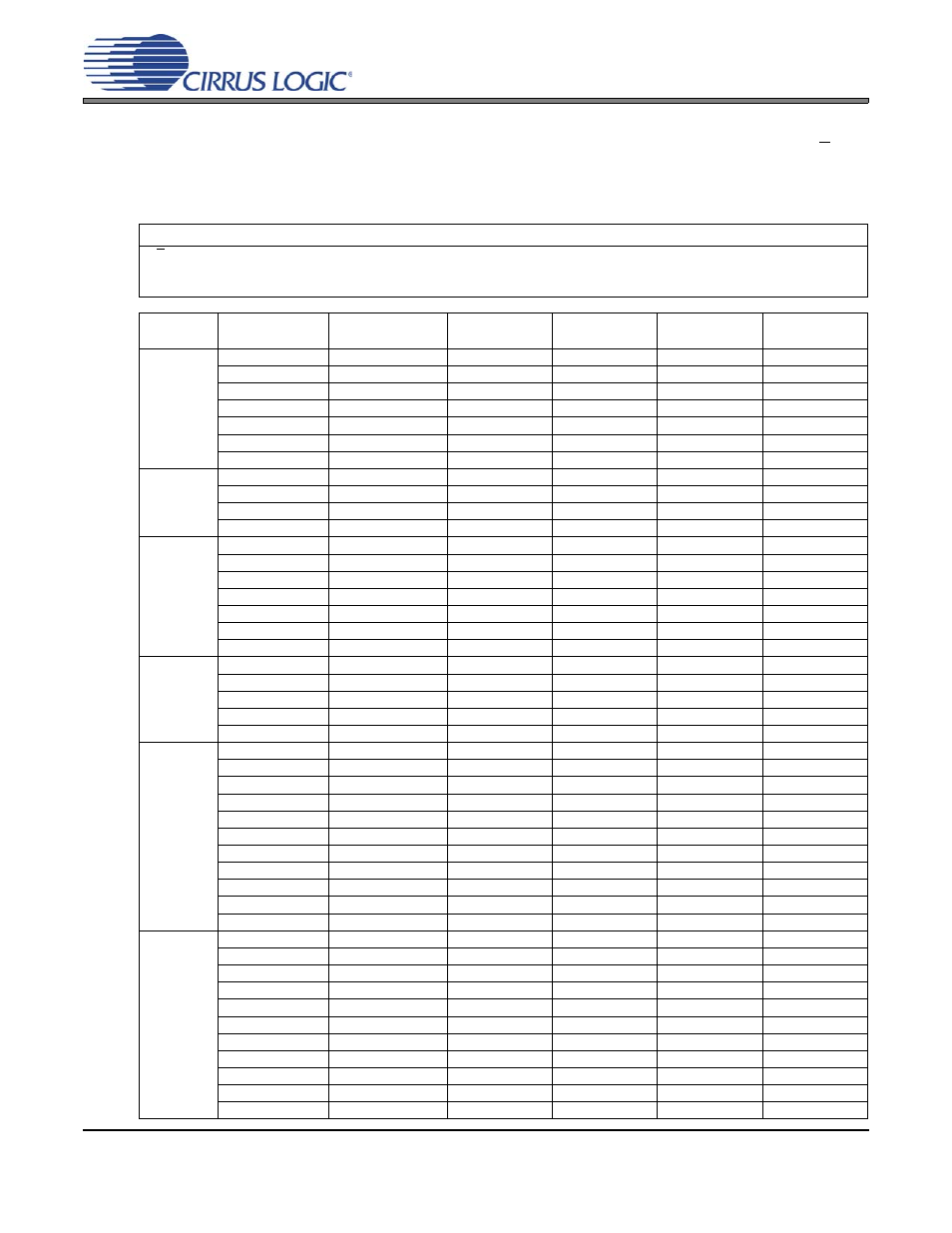

Serial Port Clocking

The CS43L22 serial audio interface port operates either as a slave or master, determined by the M/S bit. It

accepts externally generated clocks in Slave Mode and will generate synchronous clocks derived from an

input master clock (MCLK) in Master Mode. Refer to the tables below for the required setting in register 05h

and 06h associated with a given MCLK and sample rate.

Referenced Control

Register Location

M/S...................................

Register 05h......................

Register 06h......................

“Master/Slave Mode” on page 40

“Clocking Control (Address 05h)” on page 38

“Interface Control 1 (Address 06h)” on page 40

MCLK

(MHz)

Sample Rate,

Fs (kHz)

SPEED[1:0]

(AUTO=’0’b)

32kGROUP

VIDEOCLK

RATIO[1:0]

MCLKDIV2

12.2880

8.0000

11

1

0

00

0

12.0000

11

0

0

00

0

16.0000

10

1

0

00

0

24.0000

10

0

0

00

0

32.0000

01

1

0

00

0

48.0000

01

0

0

00

0

96.0000

00

0

0

00

0

11.2896

11.0250

11

0

0

00

0

22.0500

10

0

0

00

0

44.1000

01

0

0

00

0

88.2000

00

0

0

00

0

18.4320

(Slave

Mode

ONLY)

8.0000

11

1

0

00

0

12.0000

11

0

0

00

0

16.0000

10

1

0

00

0

24.0000

10

0

0

00

0

32.0000

01

1

0

00

0

48.0000

01

0

0

00

0

96.0000

00

0

0

00

0

16.9344

(Slave

Mode

ONLY)

*8.0182...

11

0

0

10

0

11.0250

11

0

0

00

0

22.0500

10

0

0

00

0

44.1000

01

0

0

00

0

88.2000

00

0

0

00

0

12.0000

8.0000

11

1

0

01

0

*11.0294...

11

0

0

11

0

12.0000

11

0

0

01

0

16.0000

10

1

0

01

0

*22.0588...

10

0

0

11

0

24.0000

10

0

0

01

0

32.0000

01

1

0

01

0

*44.1176...

01

0

0

11

0

48.0000

01

0

0

01

0

*88.2353...

00

0

0

11

0

96.0000

00

0

0

01

0

24.0000

8.0000

11

1

0

01

1

*11.0294...

11

0

0

11

1

12.0000

11

0

0

01

1

16.0000

10

1

0

01

1

*22.0588...

10

0

0

11

1

24.0000

10

0

0

01

1

32.0000

01

1

0

01

1

*44.1176...

01

0

0

11

1

48.0000

01

0

0

01

1

*88.2353...

00

0

0

11

1

96.0000

00

0

0

01

1