Table 8. revision table, Cs4398 – Cirrus Logic CS4398 User Manual

Page 45

DS568F1

45

CS4398

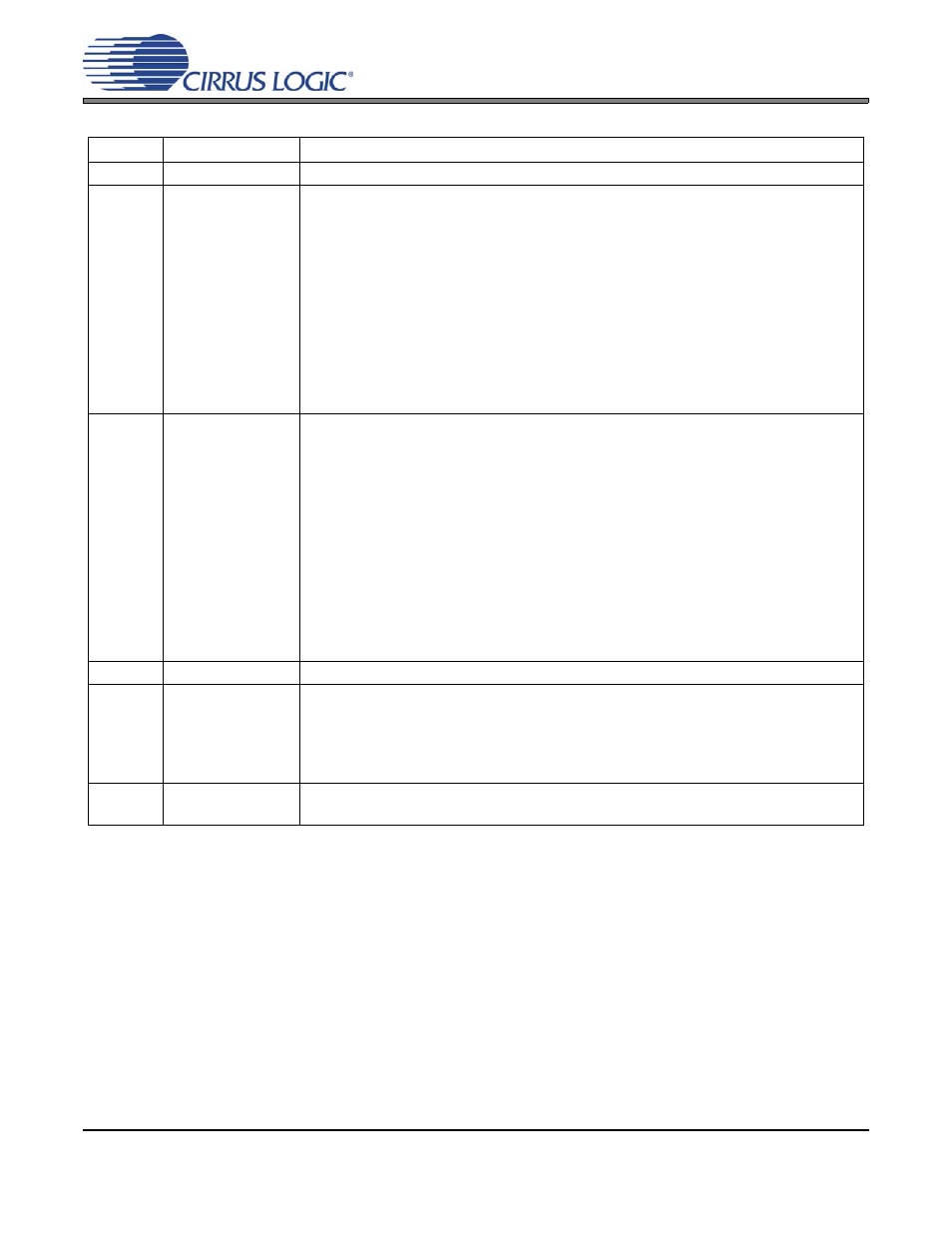

Table 8. Revision Table

Release

Date

Changes

A1

November 2002

Initial Release

PP1

July 2003

-Updated Legal Notice on page 46.

-Moved Min/Max/Typ spec note from “ANALOG CHARACTERISTICS” (on

page 9) to “CHARACTERISTICS AND SPECIFICATIONS” on page 8.

-Changed heading “RECOMMENDED OPERATING CONDITIONS” to “SPECI-

FIED OPERATING CONDITIONS” on page 8.

-Updated Full-scale Output Specifications on page 9

-Updated FILT+ nominal Voltage Specification on page 17

-Added control port note to Table 1 on page 21

-Added 64x MCLK ratio note to Table 2 on page 22

-Changed default value of DIF0 in register 02h on page 28 and

-Updated the definition of the “Digital Volume Control (VOL7:0) Bits 7-0” on

page 34

PP2

February 2004

-Updated front page block diagram

-Updated front page THD+N spec

-Added Note for -CZZ package option

-Updated Legal Notice

-Corrected 768x mode in tables 1 and 2 to use MCLKDIV2

-Added note for 0 dB-SACD to ANALOG CHARACTERISTICS

-Updated Typ and Max THD+N specs

-Updated Full-scale output levels

-Updated VIL spec

-Updated VOH and VOL levels and conditions

-Updated Max sample rate specs

-Updated recommended FILT+ capacitor value in Typical Connection Diagram

-Corrected ATAPI table values 19d and 23d

PP3

September 2004

Updated DS w/ lead-free device ordering info.

PP4

May 2005

-Removed -CZ ordering option (PCN_0044 dated Jan. 2005)

-Improved Interchannel Isolation specification

-Updated analog output impedance

-Corrected Ramp_UP and Ramp_DN bit descriptions

-Updated legal text

F1

July 2005

-Changed datasheet status to Final

-Updated legal text