1 chip id - register 01h, 2 mode control 1 - register 02h, 1 dsd input source select (dsd_src) bit 7 – Cirrus Logic CS4398 User Manual

Page 29: 2 digital interface format (dif2:0) bits 6-4, Table 5. digital interface formats - pcm mode, E register de- scription se, E register description, Cs4398, Register description

DS568F1

29

CS4398

7.

REGISTER DESCRIPTION

** All register access is R/W unless specified otherwise**

7.1

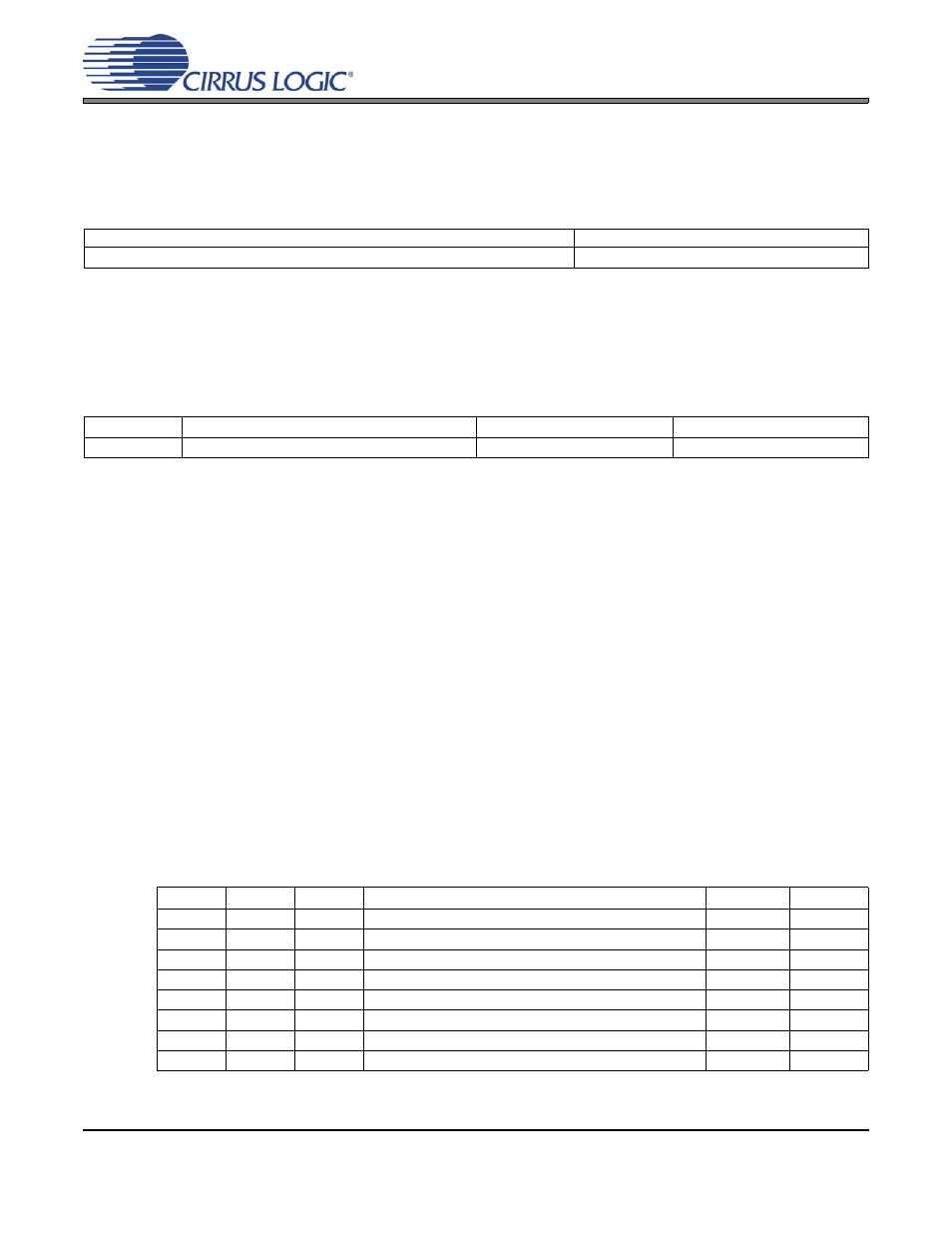

Chip ID - Register 01h

Function:

This register is Read-Only. Bits 7 through 3 are the part number ID, which is 01110b (14h), and the remain-

ing Bits (2 through 0) are for the chip revision (Rev. A = 000, Rev. B = 001, ...)

7.2

Mode Control 1 - Register 02h

7.2.1

DSD Input Source Select (DSD_SRC) BIT 7

Function:

When set to 0 (default), the dedicated DSD pins will be the active DSD inputs.

When set to 1, the source for DSD inputs will be as follows:

DSDA input on SDATA pin

DSDB input on LRCK pin

DSD_SCLK input on SCLK pin

The dedicated DSD pins must be tied low while not in use.

7.2.2

Digital Interface Format (DIF2:0) BITs 6-4

Function:

These bits select the interface format for the serial audio input. The Functional Mode bits determine

whether PCM or DSD mode is selected.

PCM Mode: The required relationship between the Left/Right clock, serial clock and serial data is defined

by the Digital Interface Format, and the options are detailed in Figures 3 through 5.

7

6

5

4

3

2

1

0

PART4

PART3

PART2

PART1

PART0

REV2

REV1

REV0

0

1

1

1

0

-

-

-

7

6

5

4

3

2

1

0

DSD_SRC

DIF2

DIF1

DIF0

DEM1

DEM0

FM1

FM0

0

0

0

0

0

0

0

0

DIF2

DIF1

DIF0

Description

Format

Figure

0

0

0

Left-Justified, up to 24-bit data

0

(Default)

0

0

1

I²S, up to 24-bit data

1

0

1

0

Right-Justified, 16-bit data

2

0

1

1

Right-Justified, 24-bit data

3

1

0

0

Right-Justified, 20-bit data

4

1

0

1

Right-Justified, 18-bit data

5

1

1

0

Reserved

1

1

1

Reserved

Table 5. Digital Interface Formats - PCM Mode