Control port interface, 1 memory address pointer (map), 1 memory address pointer (map) register detail – Cirrus Logic CS4398 User Manual

Page 25: 2 incr (auto map increment enable), 3 map3-0 (memory address pointer), 2 enabling the control port, 3 format selection, 4 i2c format

DS568F1

25

CS4398

5. CONTROL PORT INTERFACE

The Control Port is used to load all the internal settings. The operation of the Control Port may be completely asyn-

chronous with the audio sample rate. However, to avoid potential interference problems, the Control Port pins should

remain static if no operation is required.

5.1

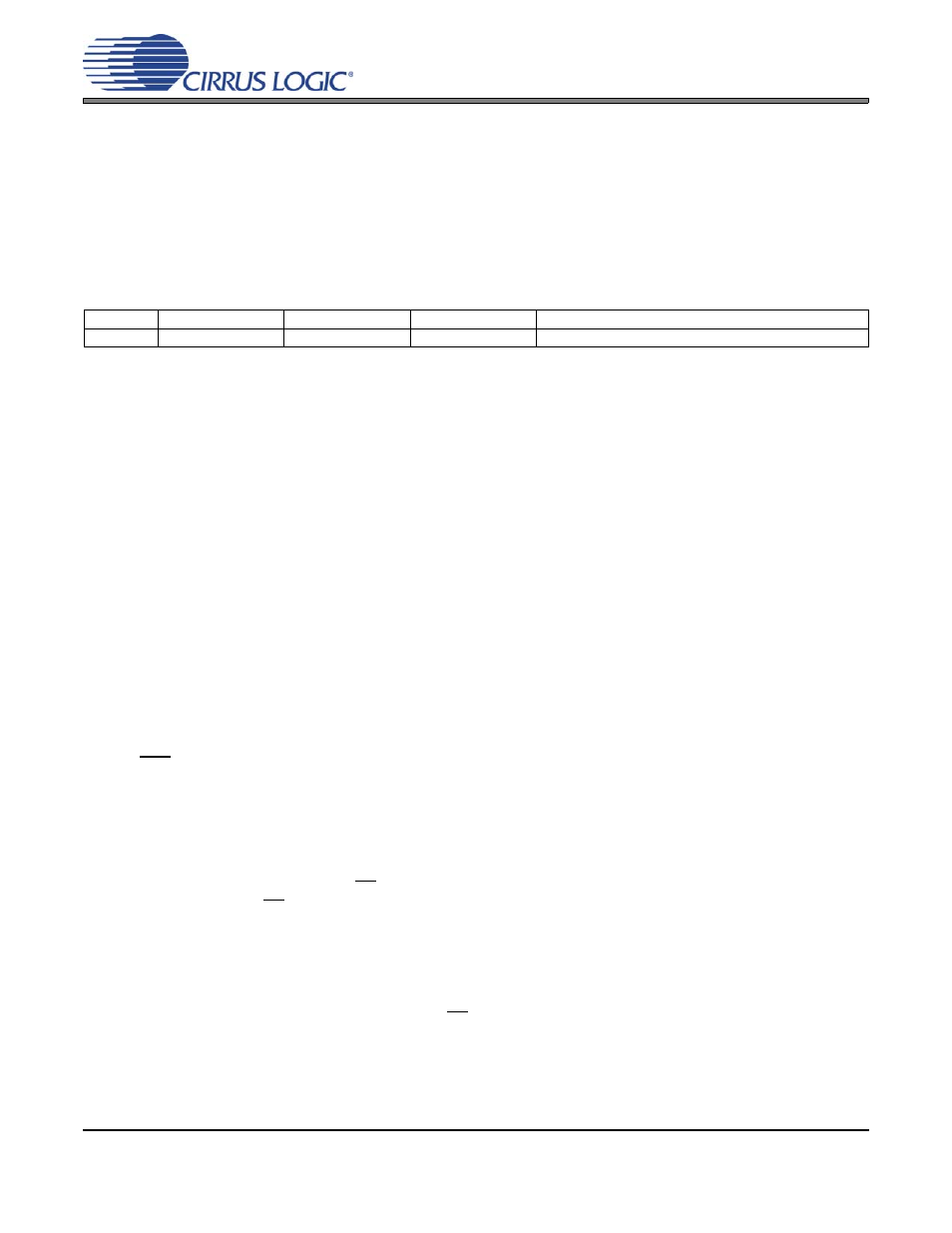

Memory Address Pointer (MAP)

5.1.1

Memory Address Pointer (MAP) Register Detail

5.1.2

INCR (Auto Map Increment Enable)

Default = ‘0’

0 - Disabled, the MAP will stay constant for successive writes

1 - Enabled, the MAP will auto increment after each byte is written, allowing block reads or writes of suc-

cessive registers

5.1.3

MAP3-0 (Memory Address Pointer)

Default = ‘0000’

5.2

Enabling the Control Port

On the CS4398, the Control Port pins are shared with Stand-Alone configuration pins. To enable the Control

Port, the user must set the CPEN bit. This is done by performing an I²C or SPI write. Once the Control Port

is enabled, these pins are dedicated to Control Port functionality.

To prevent audible artifacts, the CPEN bit (see Section 7) should be set prior to the completion of the Stand-

Alone power-up sequence, approximately 2

18

MCLK cycles. Setting this bit halts the stand-alone power-up

sequence and initializes the Control Port to its default settings. Note, the CPEN bit can be set any time after

RST goes high; however, setting this bit after the stand-alone power-up sequence has completed can cause

audible artifacts.

5.3

Format Selection

The Control Port has two formats: SPI and I²C, with the CS4398 operating as a slave device.

If I²C operation is desired, AD0/CS should be tied to VLC or GND. If the CS4398 ever detects a high-to-low

transition on AD0/CS after power-up, SPI format will automatically be selected.

5.4

I²C Format

In I²C Format, SDA is a bidirectional data line. Data is clocked into and out of the part by the clock, SCL,

with a clock-to-data relationship as shown in Figure 14. The receiving device should send an acknowledge

(ACK) after each byte received. There is no CS pin. Pins AD0 and AD1 form the partial chip address and

should be tied to VLC or GND as required. The upper five bits of the 7-bit address field must be 10011.

7

6

5

4

3

2

1

0

INCR

Reserved

Reserved

Reserved

MAP3

MAP2

MAP1

MAP0

0

0

0

0

0

0

0

0