Cirrus Logic CS4391A User Manual

Preliminary product information, Features, Description

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1

Copyright

©

Cirrus Logic, Inc. 2004

(All Rights Reserved)

www.cirrus.com

CS4391A

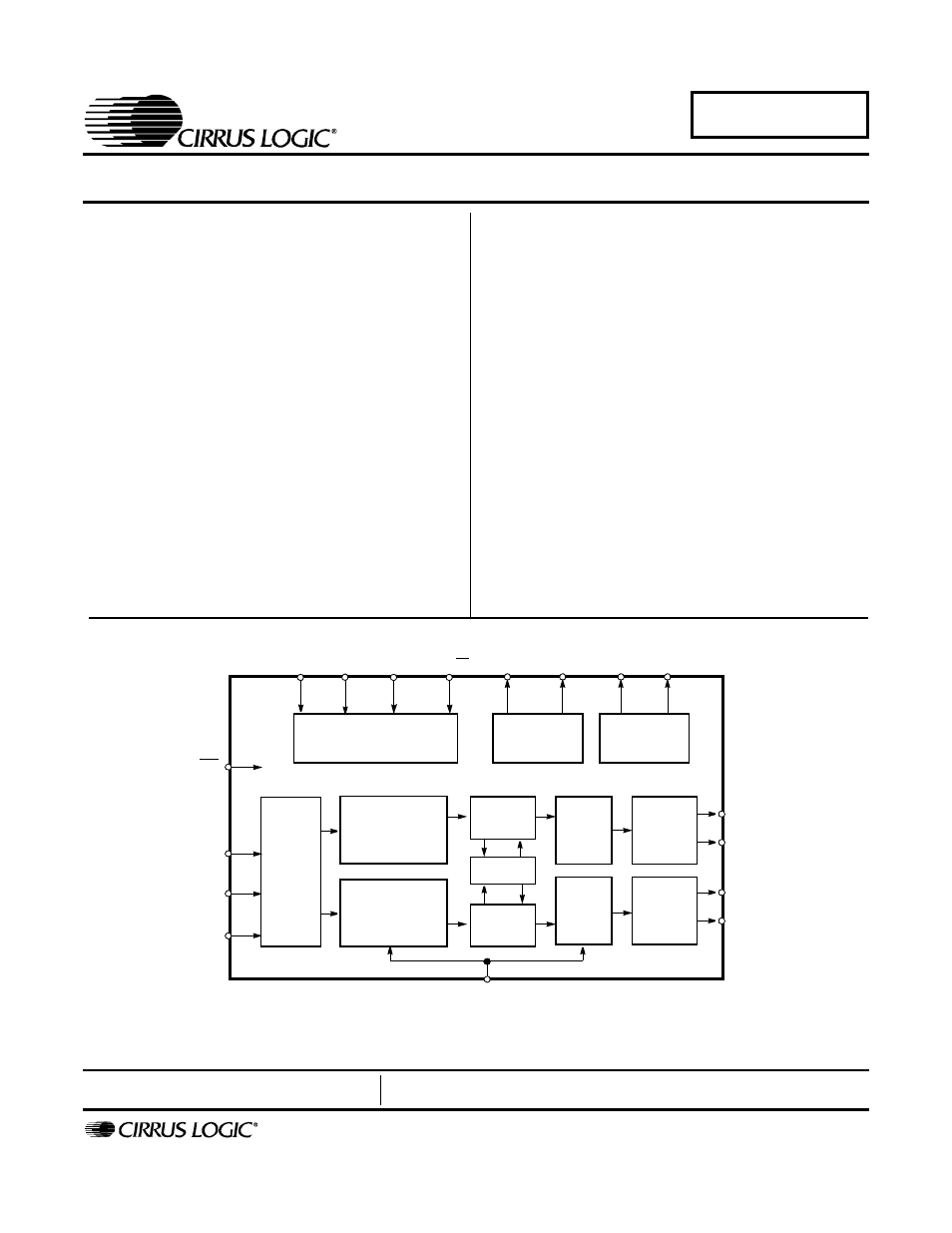

24-Bit, 192 kHz Stereo DAC with Volume Control

Features

Complete Stereo DAC System: Interpolation,

D/A, Output Analog Filtering

108 dB Dynamic Range

94 dB THD+N

Direct Stream Digital Mode

Low Clock Jitter Sensitivity

+5 V Power Supply

ATAPI Mixing

On-Chip Digital De-emphasis for 32, 44.1,

and 48 kHz

Volume Control with Soft Ramp

– 119 dB Attenuation

– 1 dB Step Size

– Zero Crossing Click-Free Transitions

Direct Interface with 5 V to 1.8 V Logic

Description

The CS4391A is a complete stereo digital-to-analog sys-

tem including digital interpolation, fourth-order delta-

sigma digital-to-analog conversion, digital de-emphasis,

volume control, channel mixing and analog filtering. The

advantages of this architecture include: ideal differential

linearity, no distortion mechanisms due to resistor

matching errors, no linearity drift over time and tempera-

ture and a high tolerance to clock jitter.

The CS4391A accepts PCM data at sample rates from

4 kHz to 192 kHz, DSD audio data, consumes very little

power and operates over a wide power supply range.

These features are ideal for DVD, A/V receivers, CD and

set-top box systems.

ORDERING INFORMATION

CS4391A-KS 20-pin SOIC

-10 to 70 °C

CS4391A-KZ 20-pin TSSOP

-10 to 70 °C

CS4391A-KZZ 20-pin TSSOP, Lead Free -10 to 70 °C

CDB4391A

Evaluation Board

I

LRCK

SDATA

(SDA/CDIN)

MCLK

AMUTEC

AOUTA-

AOUTB-

SERIAL

PORT

INTERPOLATION

INTERPOLATOR

(CONTROL PORT)

∆Σ

DAC

DAC

EXTERNAL

ANALOG

FILTER

ANALOG

FILTER

∆Σ

MUTE CONTROL

FILTER

FILTER

RST

SCLK

VOLUME

CONTROL

VOLUME

CONTROL

MIXER

(SCL/CCLK)

(AD0/CS)

AOUTA+

AOUTB+

CMOUT

REFERENCE

FILT+

BMUTEC

M1

M3

M2

MODE SELECT

M0

JUL ‘04

DS600PP3

Document Outline

- CS4391A

- Features

- Description

- 1. Characteristics/Specifications

- 2. Typical Connection Diagrams

- 3. Register Quick Reference

- 4. Register Description

- 5. Pin Description - PCM Data mode

- 6. Pin Description - DSD mode

- Table 1. Digital Interface Formats - PCM Modes

- Table 2. Digital Interface Formats - DSD Mode

- Table 3. De-Emphasis Mode Selection

- Table 4. Functional Mode Selection

- Table 5. Soft Cross or Zero Cross Mode Selection

- Table 6. ATAPI Decode

- Table 7. Digital Volume Control

- Table 8. Single Speed (4 to 50 kHz sample rates) Common Clock Frequencies

- Table 9. Double Speed (50 to 100 kHz sample rates) Common Clock Frequencies

- Table 10. Quad Speed (100 to 200 kHz sample rates) Common Clock Frequencies

- Table 11. Single Speed (4 to 50 kHz) Digital Interface Format, Stand-Alone Mode Options

- Table 12. Single Speed Only (4 to 50 kHz) De-Emphasis, Stand-Alone Mode Options

- Table 13. Double Speed (50 to 100 kHz) Digital Interface Format, Stand-Alone Mode Options

- Table 14. Quad Speed (100 to 200 kHz) Digital Interface Format, Stand-Alone Mode Options

- Table 15. Direct Stream Digital (DSD), Stand-Alone Mode Options

- Figure 7. Format 0, Left Justified up to 24-Bit Data

- Figure 8. Format 1, I2S up to 24-Bit Data

- Figure 9. Format 2, Right Justified 16-Bit Data

- Figure 10. Format 3, Right Justified 24-Bit Data

- Figure 11. Format 4, Right Justified 20-Bit Data. (Available in Control Port Mode only)

- Figure 12. Format 5, Right Justified 18-Bit Data. (Available in Control Port Mode only)

- Figure 13. De-Emphasis Curve

- Figure 14. ATAPI Block Diagram

- 7. Applications

- 8. Control Port Interface

- 8.1 SPI Mode

- 8.2 I2C Mode

- Table 16. Memory Address Pointer (MAP)

- Figure 16. Control Port Timing, SPI mode

- Figure 17. Control Port Timing, I2C Mode

- Figure 18. Single-Speed Frequency Response

- Figure 19. Single-Speed Transition Band

- Figure 20. Single-Speed Transition Band

- Figure 21. Single-Speed Stopband Rejection

- Figure 22. Double-Speed Frequency Response

- Figure 23. Double-Speed Transition Band

- Figure 24. Double-Speed Transition Band

- Figure 25. Double-Speed Stopband Rejection

- 9. Parameter Definitions

- 10. References

- 11. Package Dimensions